# **User Manual**

G32R501

Arm<sup>®</sup> Cortex<sup>®</sup>-M52 Core-based 32-bit Realtime MCU

Version: V1.2

© Geehy Semiconductor Co., Ltd.

# Contents

| 1                                                                                                                             | Introduction and document description rules                                                                                                                                                                                                                                                                                                                     | 11                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| 1.1                                                                                                                           | Introduction                                                                                                                                                                                                                                                                                                                                                    | 11                                                                         |

| 1.2                                                                                                                           | Document description rules                                                                                                                                                                                                                                                                                                                                      |                                                                            |

| 2                                                                                                                             | CPU and system architecture                                                                                                                                                                                                                                                                                                                                     | 14                                                                         |

| 2.1                                                                                                                           | Full Name and Abbreviation Description of Terms                                                                                                                                                                                                                                                                                                                 |                                                                            |

| 2.2                                                                                                                           | Introduction                                                                                                                                                                                                                                                                                                                                                    |                                                                            |

| 2.3                                                                                                                           | Main characteristics                                                                                                                                                                                                                                                                                                                                            |                                                                            |

| 2.4                                                                                                                           | Structure block diagram                                                                                                                                                                                                                                                                                                                                         |                                                                            |

| 2.5                                                                                                                           | Functional description                                                                                                                                                                                                                                                                                                                                          |                                                                            |

| 2.6                                                                                                                           | Register bank address                                                                                                                                                                                                                                                                                                                                           |                                                                            |

| 2.7                                                                                                                           | Register address mapping                                                                                                                                                                                                                                                                                                                                        |                                                                            |

| 2.8                                                                                                                           | Register functional description                                                                                                                                                                                                                                                                                                                                 |                                                                            |

| 3                                                                                                                             | Mathematics instruction extension (Zidian)                                                                                                                                                                                                                                                                                                                      | 41                                                                         |

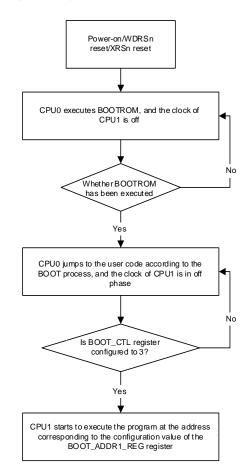

| 4                                                                                                                             | System Boot (BOOT)                                                                                                                                                                                                                                                                                                                                              | 42                                                                         |

| 4.1                                                                                                                           | Introduction                                                                                                                                                                                                                                                                                                                                                    |                                                                            |

| 4.2                                                                                                                           | Functional description                                                                                                                                                                                                                                                                                                                                          |                                                                            |

| 4.3                                                                                                                           | Register                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

| 5                                                                                                                             | Write register protection (WRPRT)                                                                                                                                                                                                                                                                                                                               | 44                                                                         |

| 5.1                                                                                                                           | Full Name and Abbreviation Description of Terms                                                                                                                                                                                                                                                                                                                 |                                                                            |

|                                                                                                                               | Introduction                                                                                                                                                                                                                                                                                                                                                    |                                                                            |

| 5.2                                                                                                                           | Introduction                                                                                                                                                                                                                                                                                                                                                    |                                                                            |

| 5.2<br>5.3                                                                                                                    | Main characteristics                                                                                                                                                                                                                                                                                                                                            |                                                                            |

|                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                 |                                                                            |

| 5.3                                                                                                                           | Main characteristics                                                                                                                                                                                                                                                                                                                                            | 44<br>44                                                                   |

| 5.3<br>5.4                                                                                                                    | Main characteristics<br>Functional description                                                                                                                                                                                                                                                                                                                  | 44<br>44<br>45                                                             |

| 5.3<br>5.4<br>5.5                                                                                                             | Main characteristics<br>Functional description<br>Register bank address                                                                                                                                                                                                                                                                                         | 44<br>44<br>45<br>46                                                       |

| 5.3<br>5.4<br>5.5<br>5.6                                                                                                      | Main characteristics<br>Functional description<br>Register bank address<br>Register address mapping                                                                                                                                                                                                                                                             |                                                                            |

| 5.3<br>5.4<br>5.5<br>5.6<br>5.7                                                                                               | Main characteristics<br>Functional description<br>Register bank address<br>Register address mapping<br>Register functional description                                                                                                                                                                                                                          |                                                                            |

| 5.3<br>5.4<br>5.5<br>5.6<br>5.7<br><b>6</b>                                                                                   | Main characteristics<br>Functional description<br>Register bank address<br>Register address mapping<br>Register functional description<br>UID                                                                                                                                                                                                                   |                                                                            |

| 5.3<br>5.4<br>5.5<br>5.6<br>5.7<br><b>6</b><br>6.1                                                                            | Main characteristics<br>Functional description<br>Register bank address<br>Register address mapping<br>Register functional description<br><b>UID</b><br>Register bank address                                                                                                                                                                                   |                                                                            |

| 5.3<br>5.4<br>5.5<br>5.6<br>5.7<br><b>6</b><br>6.1<br>6.2                                                                     | Main characteristics<br>Functional description<br>Register bank address<br>Register address mapping<br>Register functional description<br><b>UID</b><br>Register bank address<br>Register address mapping                                                                                                                                                       | 44<br>44<br>45<br>46<br>46<br><b>46</b><br><b>47</b><br>47<br>47<br>47     |

| <ul> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>5.7</li> <li>6</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> </ul> | Main characteristics<br>Functional description<br>Register bank address<br>Register address mapping<br>Register functional description<br><b>UID</b><br>Register bank address<br>Register address mapping<br>Register functional description                                                                                                                    | 44<br>44<br>45<br>46<br>46<br>46<br>47<br>47<br>47<br>47<br>47<br>47       |

| 5.3<br>5.4<br>5.5<br>5.6<br>5.7<br><b>6</b><br>6.1<br>6.2<br>6.3<br><b>7</b>                                                  | Main characteristics<br>Functional description<br>Register bank address<br>Register address mapping<br>Register functional description<br><b>UID</b><br>Register bank address<br>Register address mapping<br>Register address mapping<br>Register functional description                                                                                        | 44<br>44<br>45<br>46<br>46<br>46<br>47<br>47<br>47<br>47<br>47<br>47<br>50 |

| 5.3<br>5.4<br>5.5<br>5.6<br>5.7<br><b>6</b><br>6.1<br>6.2<br>6.3<br><b>7</b><br><b>8</b>                                      | Main characteristics<br>Functional description<br>Register bank address<br>Register address mapping<br>Register functional description<br><b>UID</b><br>Register bank address<br>Register address mapping<br>Register address mapping<br>Register functional description<br><b>Power management</b><br><b>Device identification and configuration registers</b> |                                                                            |

| 8.4   | Register functional description                   | 51  |

|-------|---------------------------------------------------|-----|

| 9     | Low-power mode                                    | 58  |

| 9.1   | IDLE                                              |     |

| 9.2   | HALT                                              |     |

| 10    | Reset                                             | 61  |

| 10.1  | Functional description                            | 61  |

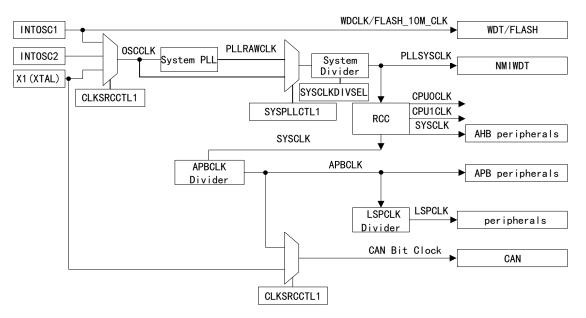

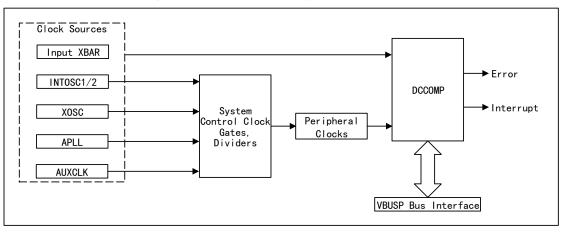

| 11    | Clock                                             | 63  |

| 11.1  | Structure block diagram                           | 63  |

| 11.2  | Functional description                            | 63  |

| 11.3  | Register bank address                             | 71  |

| 11.4  | Register address mapping                          | 72  |

| 11.5  | Register functional description                   | 72  |

| 12    | System control                                    | 79  |

| 12.1  | SPEC Functional Description                       | 79  |

| 12.2  | SPEC register bank address                        | 79  |

| 12.3  | SPEC register address mapping                     | 79  |

| 12.4  | Functional description of SPEC registers          | 80  |

| 12.5  | NMI_INTRUPT register bank address                 |     |

| 12.6  | NMI_INTRUPT register address mapping              |     |

| 12.7  | Functional description of NMI_INTRUPT registers   |     |

| 12.8  | PERIPH_AC register bank address                   |     |

| 12.9  | PERIPH_AC register address mapping                |     |

| 12.10 | Functional description of PERIPH_AC register      |     |

| 12.11 | ROM_PREFETCH register bank address                |     |

| 12.12 | ROM_PREFETCH register address mapping             |     |

| 12.13 | Functional description of ROM_PREFETCH register   | 100 |

| 12.14 | ROM_WAIT_STATE register bank address              | 100 |

| 12.15 | ROM_WAIT_STATE register address mapping           |     |

| 12.16 | Functional description of ROM_WAIT_STATE register |     |

| 13    | Nested Vector Interrupt Controller (NVIC)         | 102 |

| 13.1  | Full Name and Abbreviation Description of Terms   | 102 |

| 13.2  | Introduction                                      | 102 |

| 13.3  | Main characteristics                              | 102 |

| 13.4  | Interrupt and exception vector table              | 102 |

| 14    | External interrupt and event controller (EXTI)    | 110 |

| 14.1  | Introduction                                      | 110 |

| 14.2 | Main characteristics                            | 110 |

|------|-------------------------------------------------|-----|

| 14.3 | Functional description                          | 110 |

| 14.4 | Register bank address                           | 112 |

| 14.5 | Register address mapping                        | 112 |

| 14.6 | Register functional description                 | 113 |

| 15   | Dual Code Security (DCS)                        | 118 |

| 16   | Configurable static memory subsystem (CFGSMS)   | 119 |

| 17   | Nonvolatile memory controller (NVMC)            | 120 |

| 17.1 | Introduction                                    | 120 |

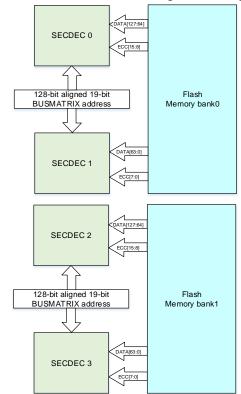

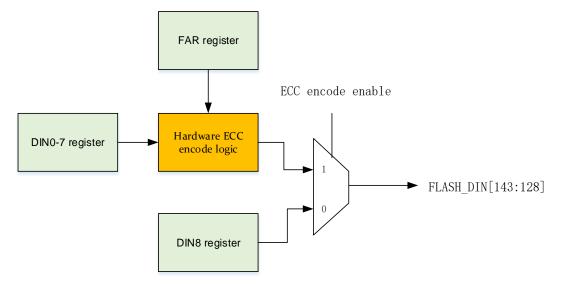

| 17.2 | Structure block diagram                         | 121 |

| 17.3 | Main characteristics                            | 122 |

| 17.4 | Functional description                          | 123 |

| 17.5 | Register bank address                           | 131 |

| 17.6 | Register address mapping                        | 132 |

| 17.7 | Register functional description                 | 133 |

| 18   | Timer 0/1/2 (TMR0/1/2)                          | 149 |

| 18.1 | Full Name and Abbreviation Description of Terms | 149 |

| 18.2 | Introduction                                    | 149 |

| 18.3 | Main characteristics                            |     |

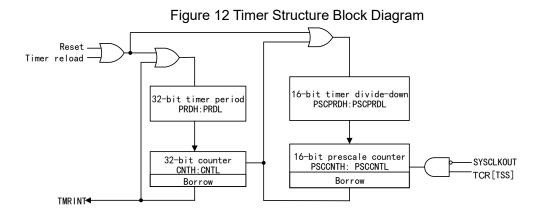

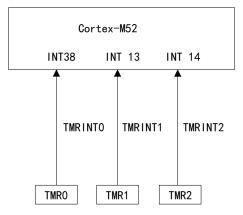

| 18.4 | Structure block diagram                         |     |

| 18.5 | Functional description                          | 150 |

| 18.6 | Register bank address                           | 150 |

| 18.7 | Register address mapping                        | 150 |

| 18.8 | Register functional description                 | 151 |

| 19   | Watchdog timer (WDT)                            | 155 |

| 19.1 | Full Name and Abbreviation Description of Terms | 155 |

| 19.2 | Introduction                                    | 155 |

| 19.3 | Main characteristics                            | 155 |

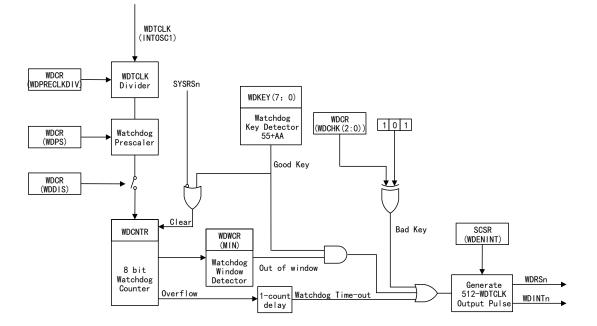

| 19.4 | Structure block diagram                         | 156 |

| 19.5 | Functional description                          | 156 |

| 19.6 | Register bank address                           | 159 |

| 19.7 | Register address mapping                        | 159 |

| 19.8 | Register functional description                 | 159 |

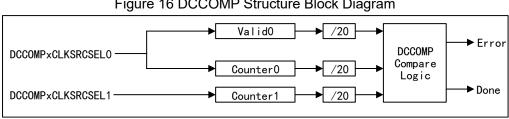

| 20   | Dual-clock comparator (DCCOMP)                  | 163 |

| 20.1 | Introduction                                    | 163 |

| 20.2 | Main characteristics                            | 163 |

| 20.3 | Structure block diagram                         |     |

|------|-------------------------------------------------|-----|

| 20.4 | Functional description                          |     |

| 20.5 | Register bank address                           |     |

| 20.6 | Register address mapping                        |     |

| 20.7 | Register functional description                 |     |

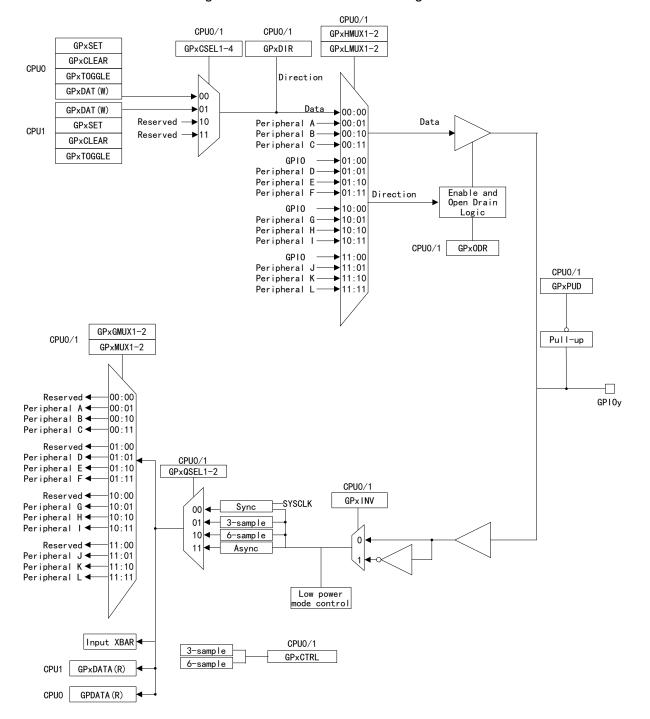

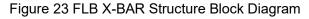

| 21   | General-Purpose Input/Output Pin (GPIO)         | 173 |

| 21.1 | Full Name and Abbreviation Description of Terms |     |

| 21.2 | Introduction                                    |     |

| 21.3 | Main characteristics                            |     |

| 21.4 | Structure block diagram                         |     |

| 21.5 | Functional description                          |     |

| 21.6 | GPIO Multiplexing Function Configuration        |     |

| 21.7 | Register bank address                           | 190 |

| 21.8 | Register address mapping                        |     |

| 21.9 | Register functional description                 |     |

| 22   | Inter-processor communication unit (IPC)        |     |

| 22.1 | Introduction                                    | 242 |

| 22.2 | Main characteristics                            | 242 |

| 22.3 | Functional description                          |     |

| 22.4 | Register address mapping                        | 246 |

| 22.5 | Register functional description                 |     |

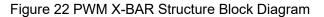

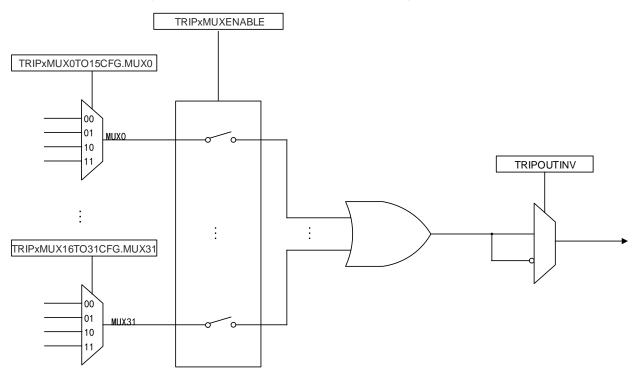

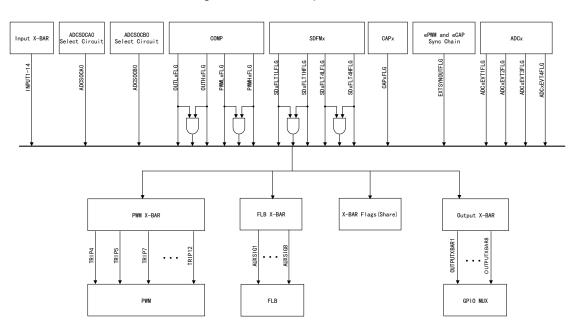

| 23   | X-BAR                                           |     |

| 23.1 | Introduction                                    |     |

| 23.2 | Main characteristics                            |     |

| 23.3 | Functional description                          |     |

| 23.4 | Register bank address                           |     |

| 23.5 | Register address mapping                        |     |

| 23.6 | Register functional description                 |     |

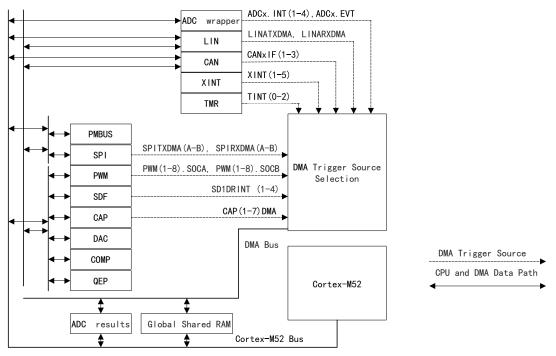

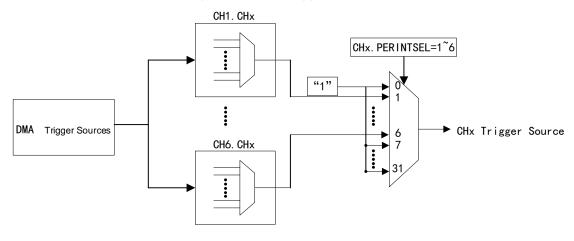

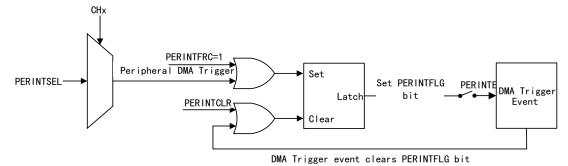

| 24   | Direct memory access (DMA)                      | 295 |

| 24.1 | Full Name and Abbreviation Description of Terms |     |

| 24.2 | Introduction                                    |     |

| 24.3 | Main characteristics                            |     |

| 24.4 | Structure block diagram                         |     |

| 24.5 | Functional description                          |     |

| 24.6 | Register bank address                           |     |

| 24.7 | Register address mapping                        |     |

| 24.8 | Register functional description                 | . 307 |

|------|-------------------------------------------------|-------|

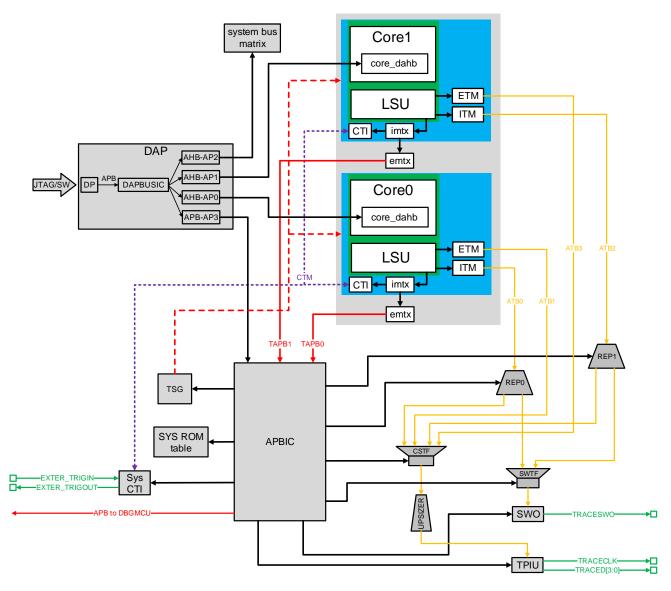

| 25   | Dual-core debug system (DCDS)                   | 321   |

| 25.1 | Full Name and Abbreviation Description of Terms | . 321 |

| 25.2 | Introduction                                    | . 321 |

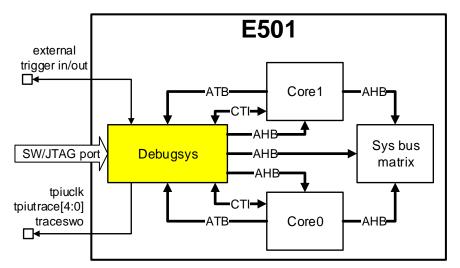

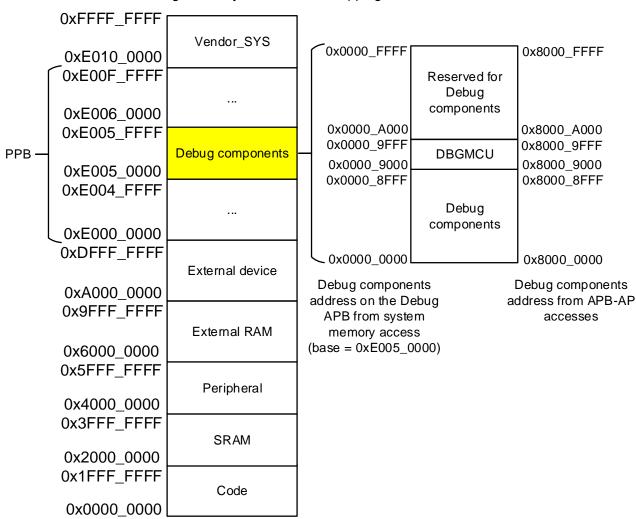

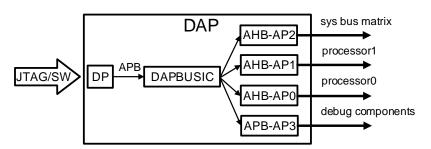

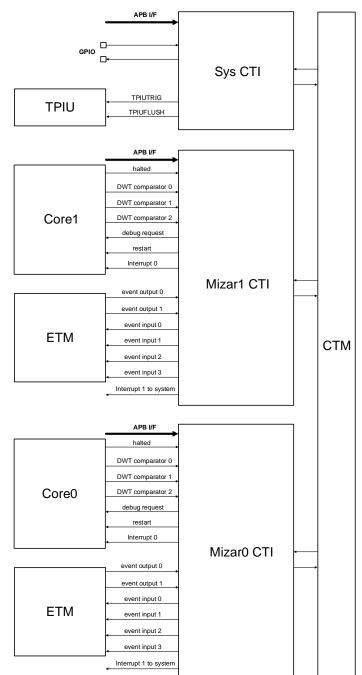

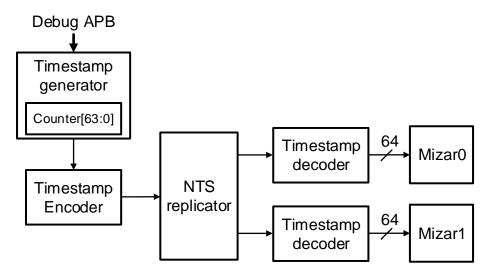

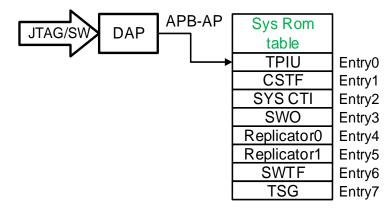

| 25.3 | Structure block diagram                         | . 322 |

| 25.4 | Main characteristics                            | . 323 |

| 25.5 | Functional description                          | . 323 |

| 26   | Analog Subsystem (AS)                           | 331   |

| 26.1 | Introduction                                    | . 331 |

| 26.2 | Main characteristics                            | . 331 |

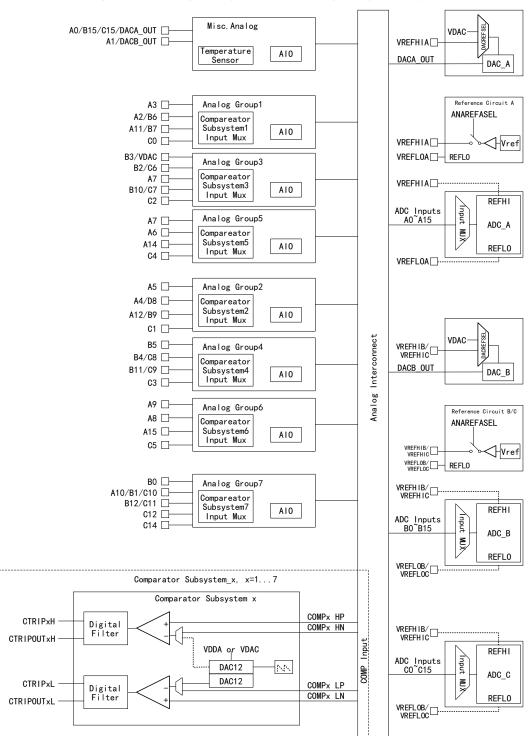

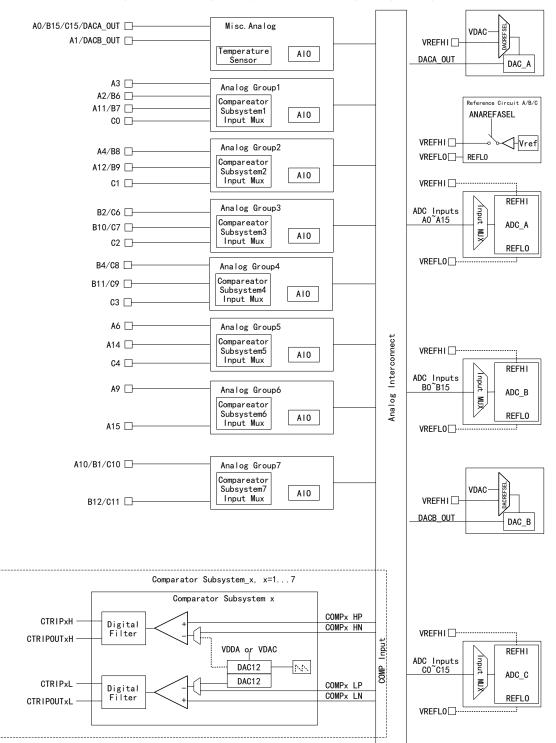

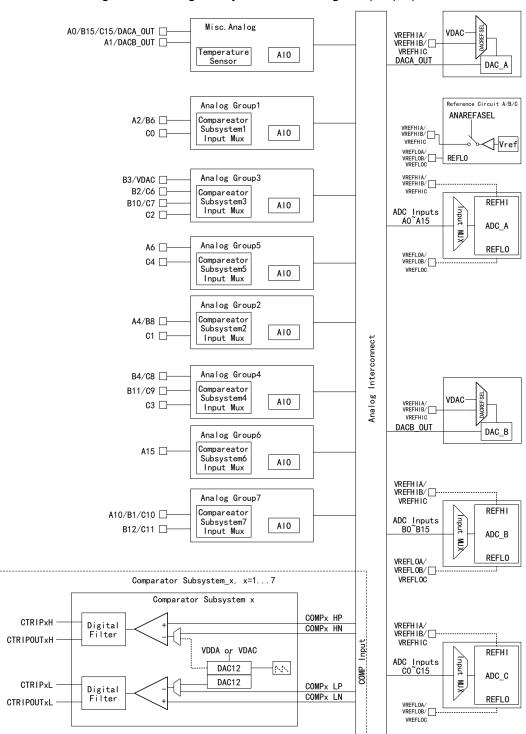

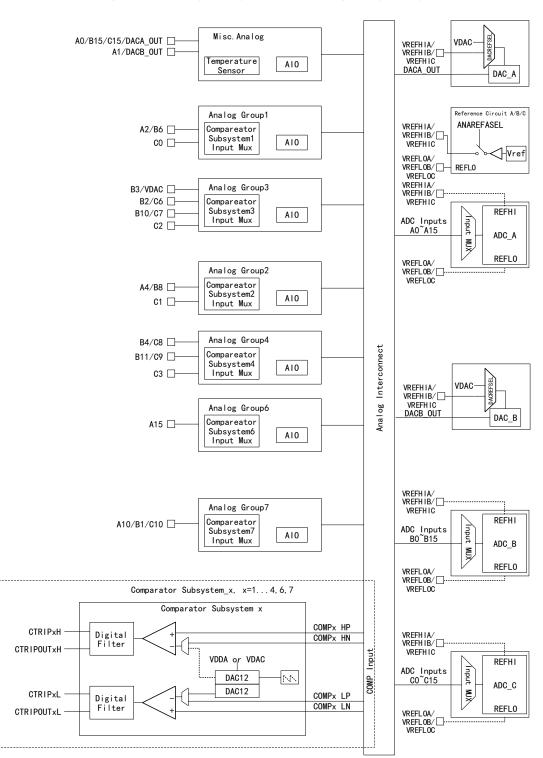

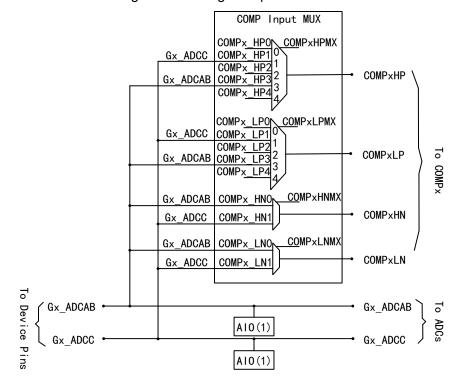

| 26.3 | Structure block diagram                         | . 331 |

| 26.4 | Functional description                          | . 337 |

| 26.5 | Register bank address                           | . 344 |

| 26.6 | Register address mapping                        | . 344 |

| 26.7 | Register functional description                 | . 344 |

| 27   | Analog-to-digital converter (ADC)               | 352   |

| 27.1 | Full Name and Abbreviation Description of Terms | . 352 |

| 27.2 | Introduction                                    | . 352 |

| 27.3 | Main characteristics                            | . 352 |

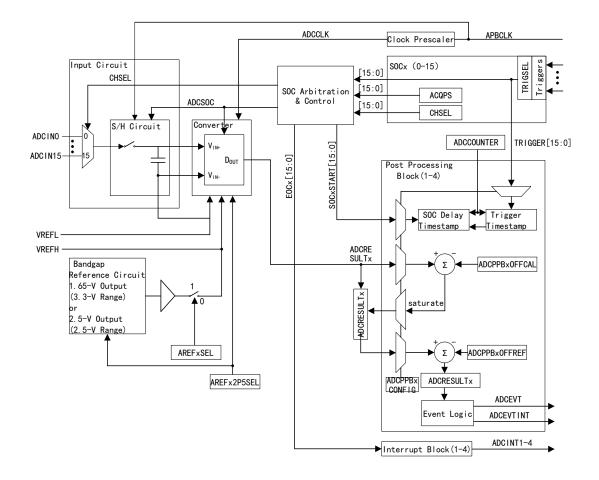

| 27.4 | Structure block diagram                         | . 353 |

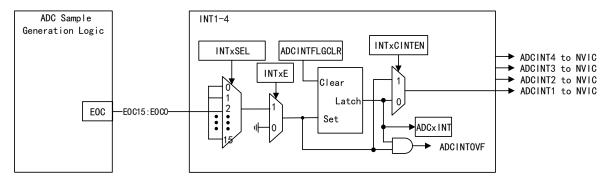

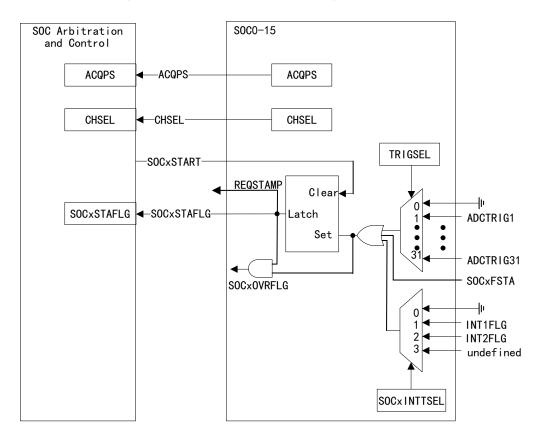

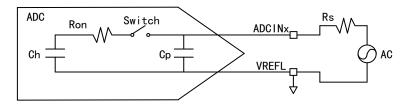

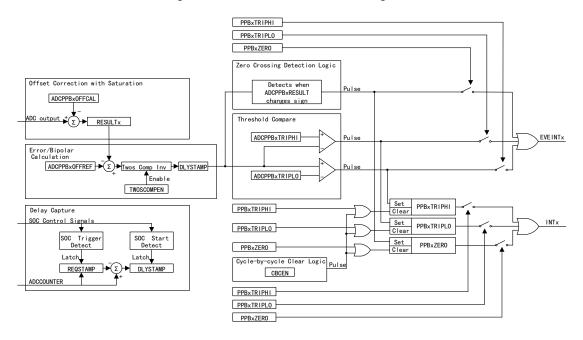

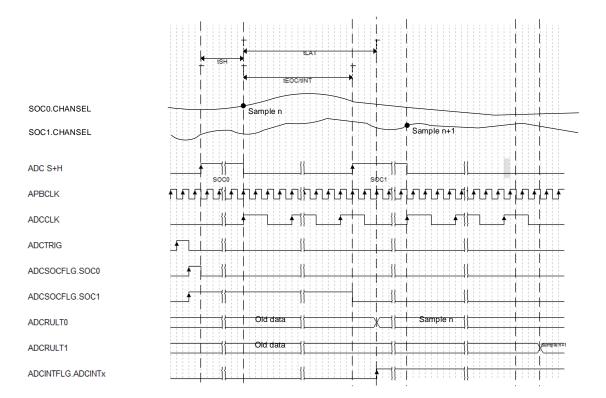

| 27.5 | Functional description                          | . 353 |

| 27.6 | Register bank address                           | . 374 |

| 27.7 | Register address mapping                        | . 374 |

| 27.8 | Register functional description                 | . 378 |

| 28   | Buffer digital-to-analog converter (DAC)        | 399   |

| 28.1 | Full Name and Abbreviation Description of Terms | . 399 |

| 28.2 | Introduction                                    | . 399 |

| 28.3 | Main characteristics                            | . 399 |

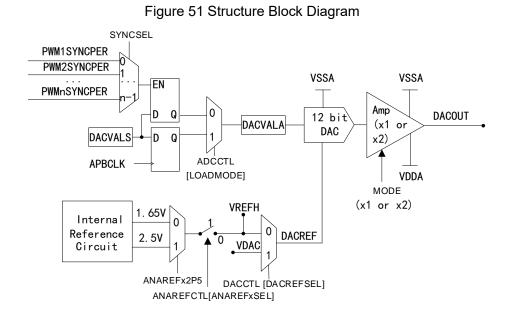

| 28.4 | Structure block diagram                         | . 399 |

| 28.5 | Functional description                          | . 400 |

| 28.6 | Lock register                                   | . 401 |

| 28.7 | Register bank address                           | . 401 |

| 28.8 | Register address mapping                        | . 402 |

| 28.9 | Register functional description                 | . 402 |

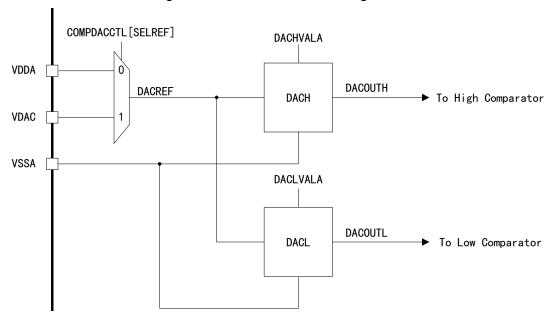

| 29   | Comparator (COMP)                               | 405   |

| 29.1 | Full Name and Abbreviation Description of Terms | . 405 |

| 29.2 | Introduction                                    | 405 |

|------|-------------------------------------------------|-----|

| 29.3 | Main characteristics                            |     |

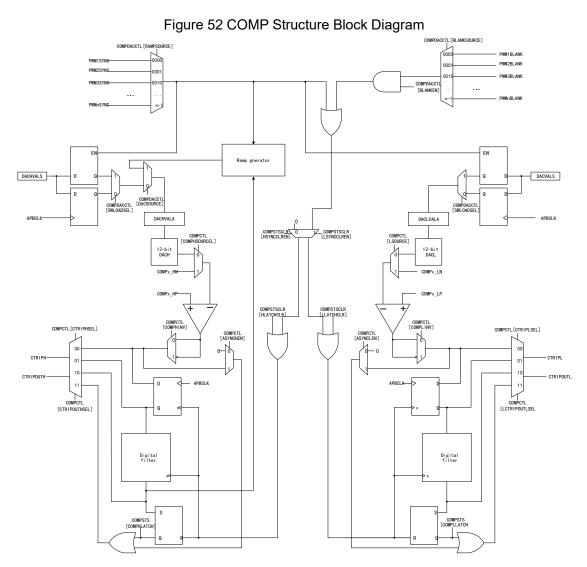

| 29.4 | Structure block diagram                         |     |

| 29.5 | Functional description                          |     |

| 29.6 | Register bank address                           | 416 |

| 29.7 | Register address mapping                        | 416 |

| 29.8 | Register functional description                 | 417 |

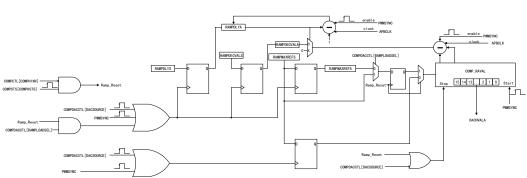

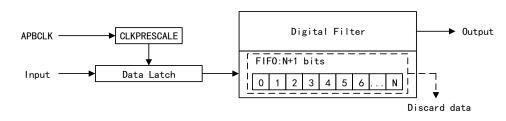

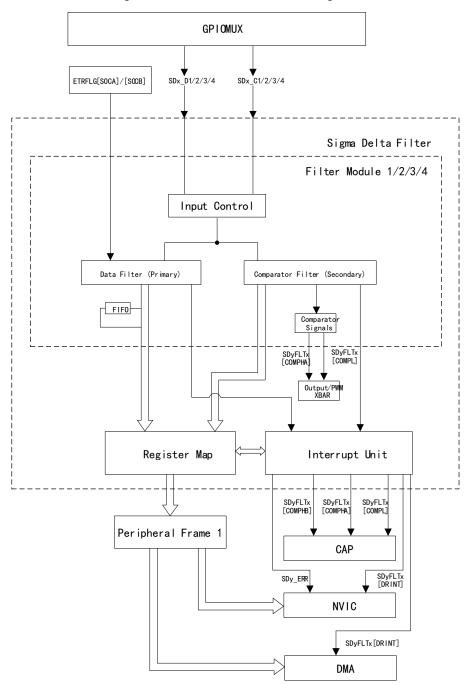

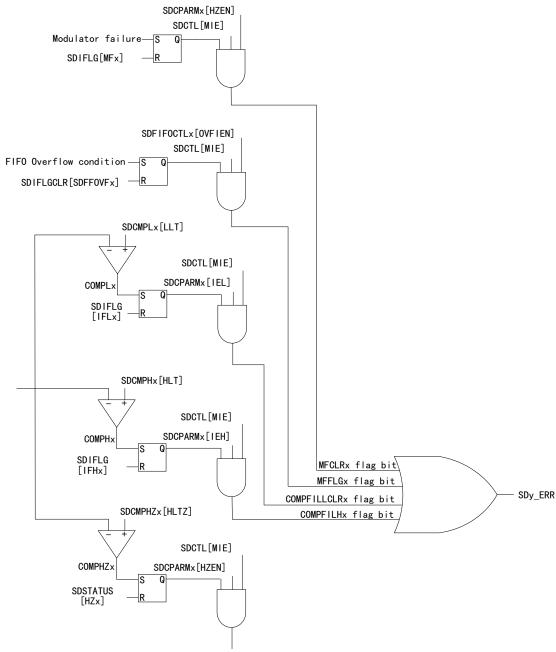

| 30   | Sigma- Delta filter (SDF)                       | 426 |

| 30.1 | Full Name and Abbreviation Description of Terms |     |

| 30.2 | Introduction                                    |     |

| 30.3 | Main characteristics                            |     |

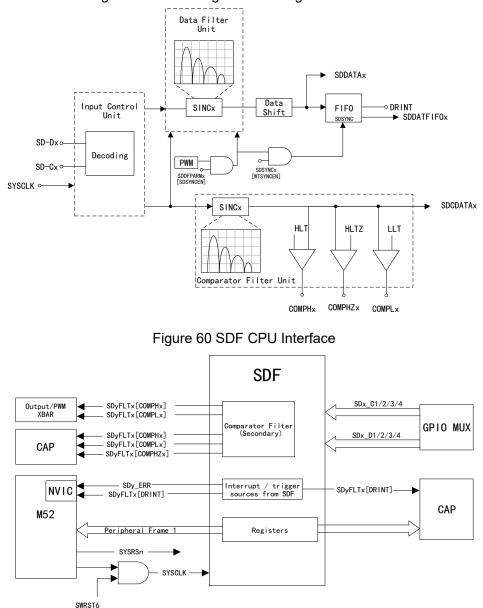

| 30.4 | Structure block diagram                         |     |

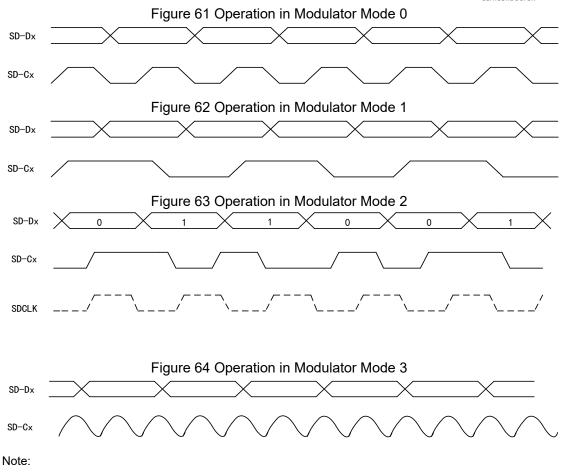

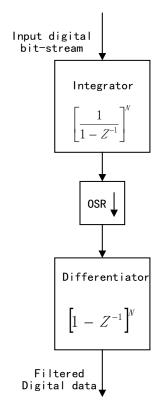

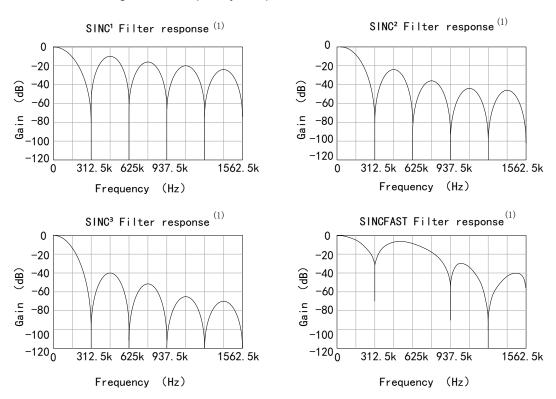

| 30.5 | Functional description                          |     |

| 30.6 | Register bank address                           |     |

| 30.7 | Register address mapping                        |     |

| 30.8 | Register functional description                 |     |

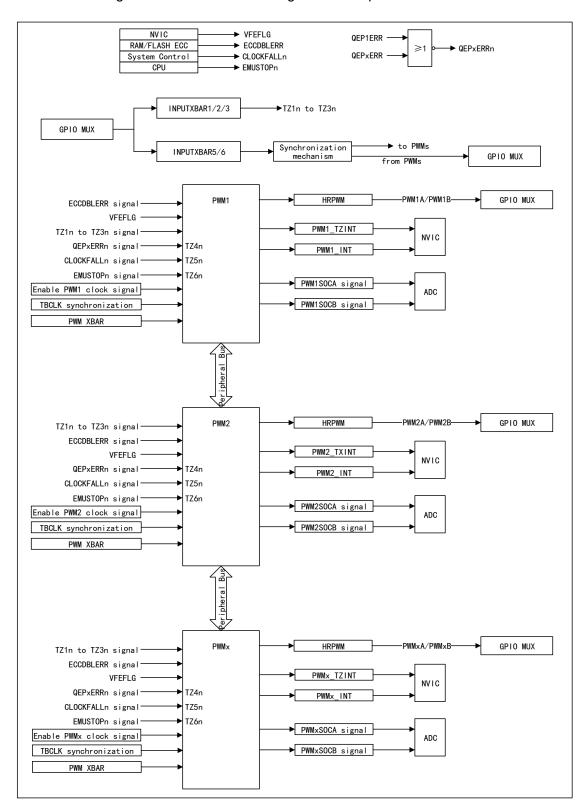

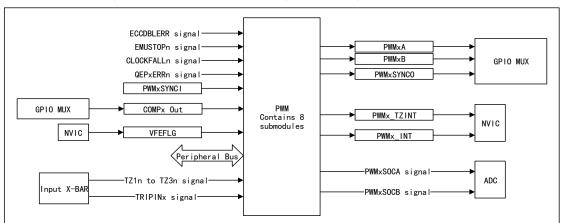

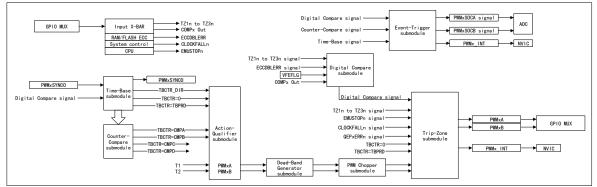

| 31   | Pulse width modulator (PWM)                     | 456 |

| 31.1 | Full Name and Abbreviation Description of Terms |     |

| 31.2 | Introduction                                    |     |

| 31.3 | Main characteristics                            |     |

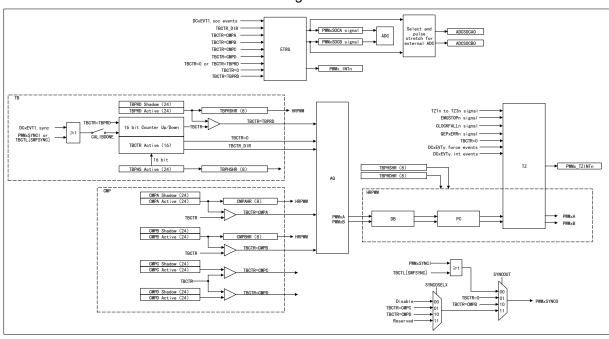

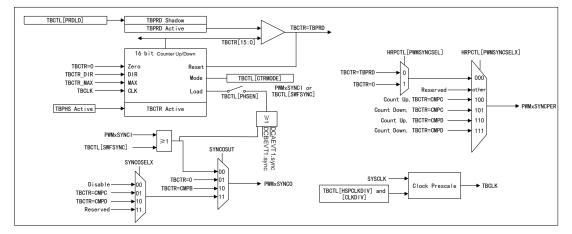

| 31.4 | Structure block diagram                         |     |

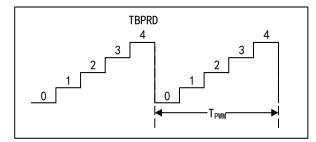

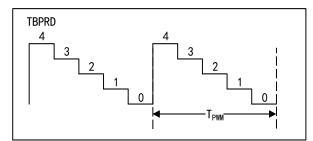

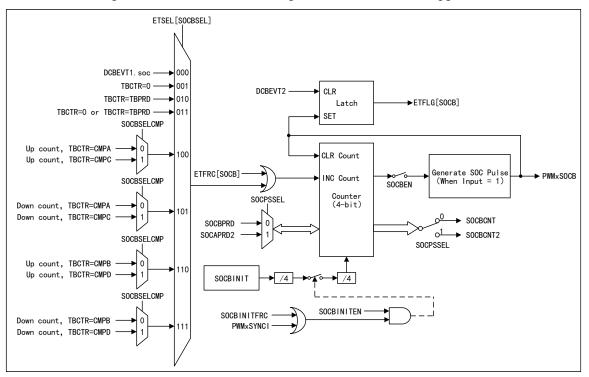

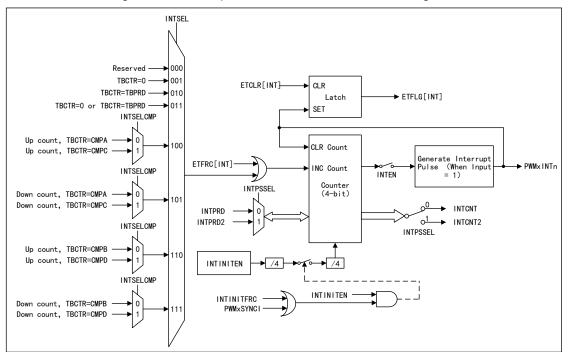

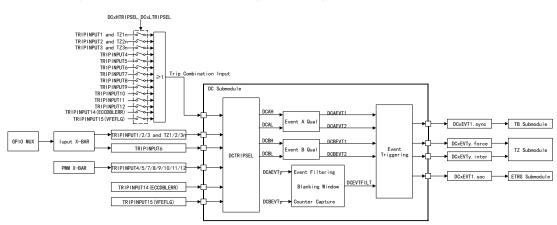

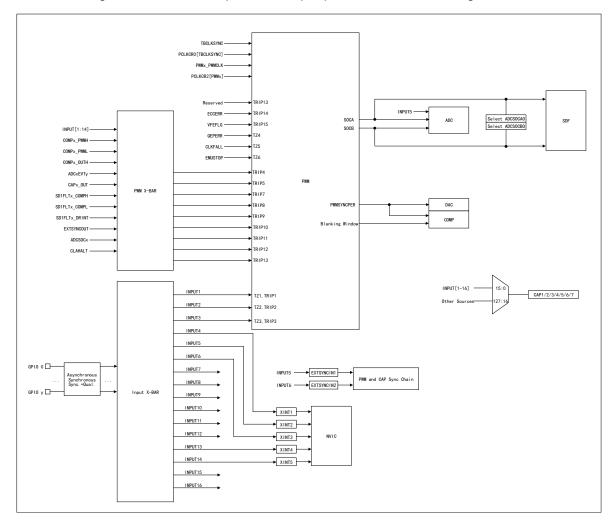

| 31.5 | Functional description                          |     |

| 31.6 | Register bank address                           | 537 |

| 31.7 | Register address mapping                        | 538 |

| 31.8 | Register functional description                 | 540 |

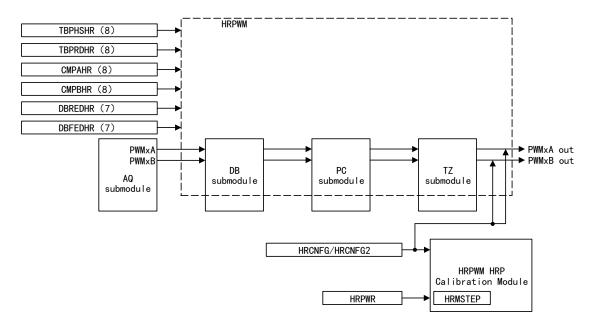

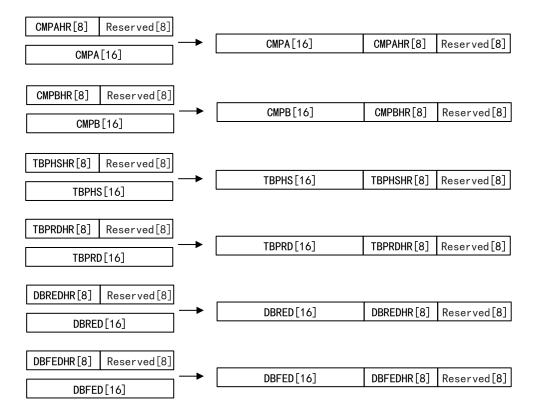

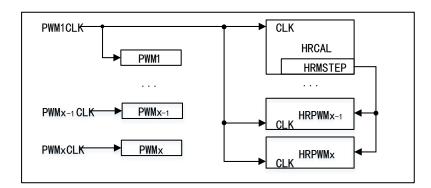

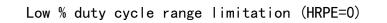

| 32   | High-resolution pulse width modulator (HRPWM)   | 609 |

| 32.1 | Full Name and Abbreviation Description of Terms | 609 |

| 32.2 | Introduction                                    | 609 |

| 32.3 | Main characteristics                            | 609 |

| 32.4 | Structure block diagram                         | 610 |

| 32.5 | Functional description                          | 610 |

| 32.6 | Register                                        | 628 |

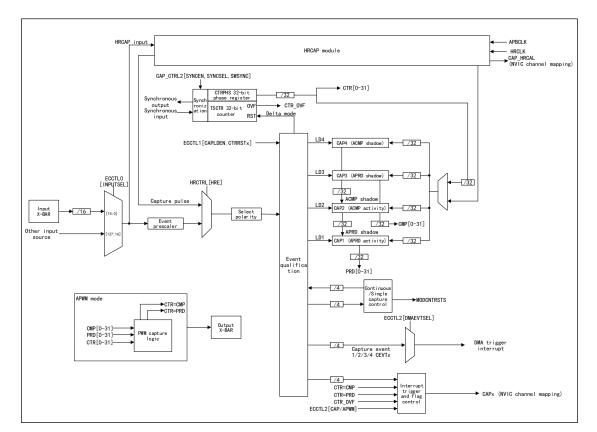

| 33   | Capture (CAP)                                   | 629 |

| 33.1 | Full Name and Abbreviation Description of Terms |     |

| 33.2 | Introduction                                    |     |

| 33.3 | Main characteristics                            |     |

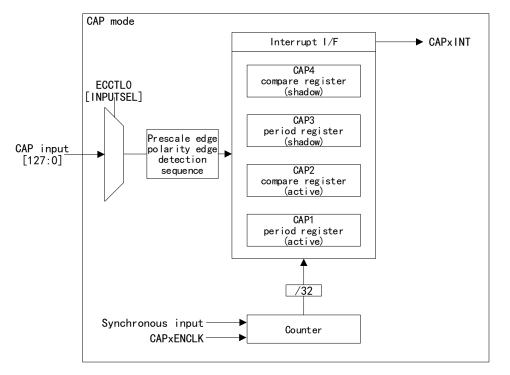

| 33.4  | Structure block diagram                                          | 631 |

|-------|------------------------------------------------------------------|-----|

| 33.5  | Function description of CAP pins                                 | 631 |

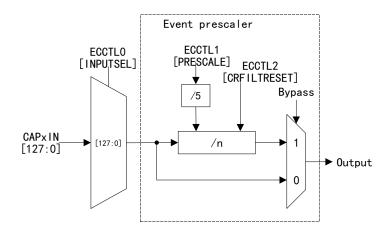

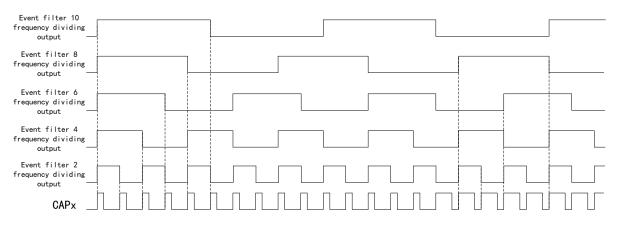

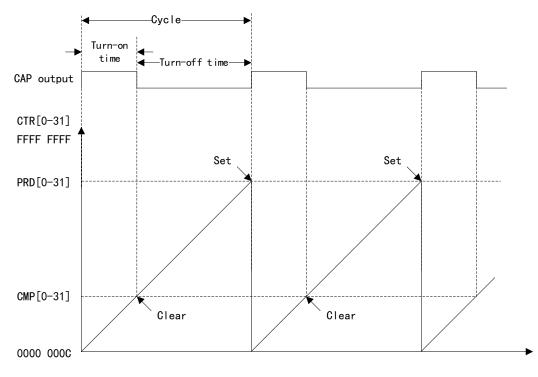

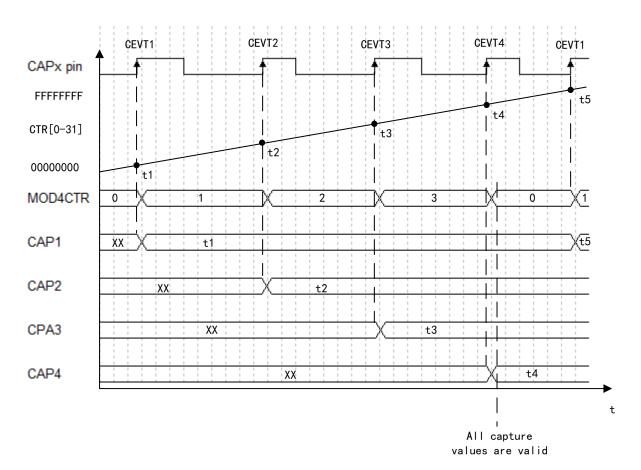

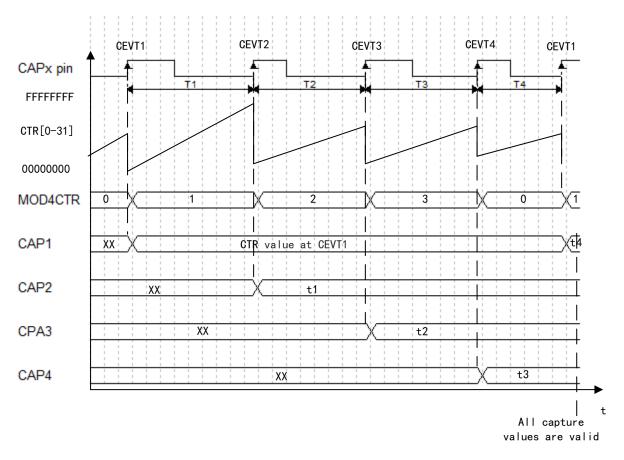

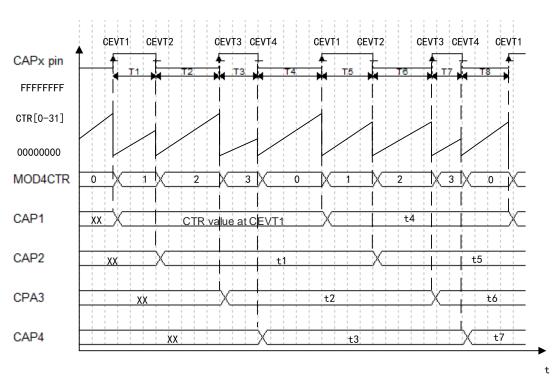

| 33.6  | Capture description function description                         | 633 |

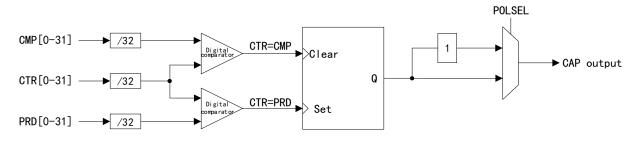

| 33.7  | Function description of APWM mode                                | 640 |

| 33.8  | CAP module application                                           | 643 |

| 33.9  | Register bank address                                            | 646 |

| 33.10 | Register address mapping                                         | 646 |

| 33.11 | Register functional description                                  | 647 |

| 34    | High-resolution capture (HRCAP)                                  | 655 |

| 34.1  | Full Name and Abbreviation Description of Terms                  | 655 |

| 34.2  | Introduction                                                     | 655 |

| 34.3  | Main characteristics                                             | 655 |

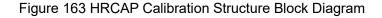

| 34.4  | Structure block diagram                                          | 656 |

| 34.5  | Functional description                                           | 656 |

| 34.6  | Register bank address                                            | 660 |

| 34.7  | Register address mapping                                         | 660 |

| 34.8  | Register functional description                                  | 660 |

| 35    | Quadrature encoder pulse (QEP)                                   | 664 |

| 35.1  | Full Name and Abbreviation Description of Terms                  |     |

| 35.2  | Introduction                                                     | 664 |

| 35.3  | Main characteristics                                             | 664 |

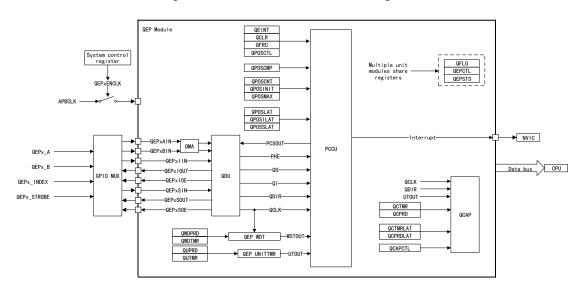

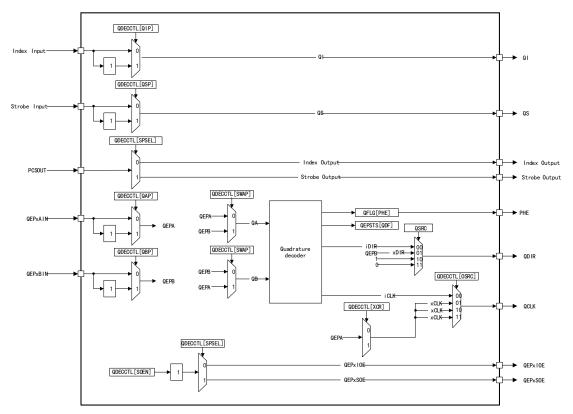

| 35.4  | Structure block diagram                                          | 665 |

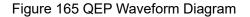

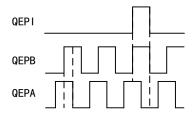

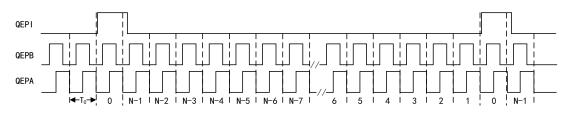

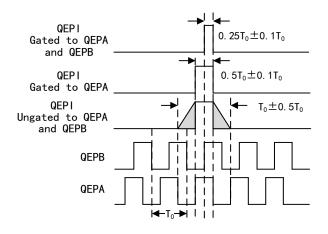

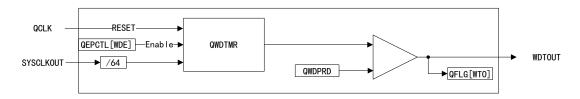

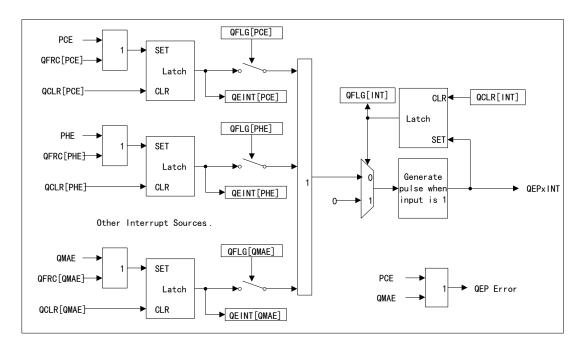

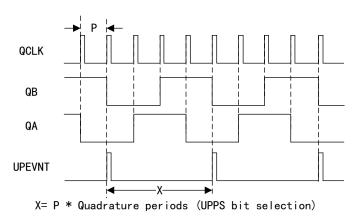

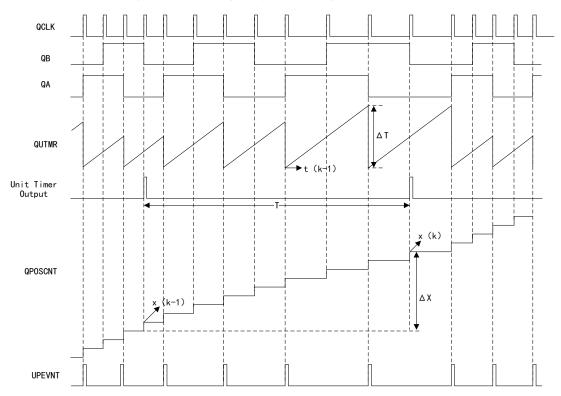

| 35.5  | Functional description                                           | 665 |

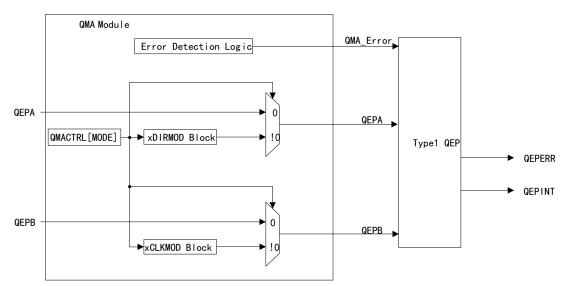

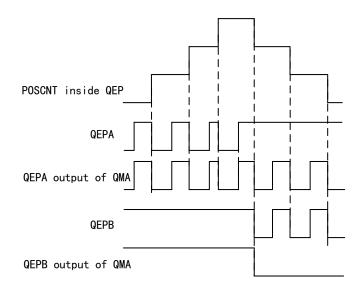

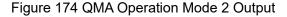

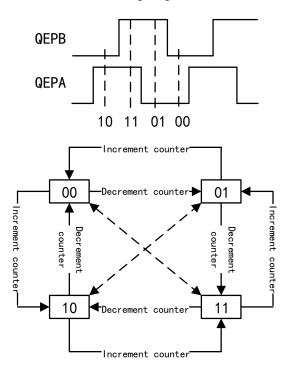

| 35.6  | Function description of quadrature mode adapter (QMA)            | 672 |

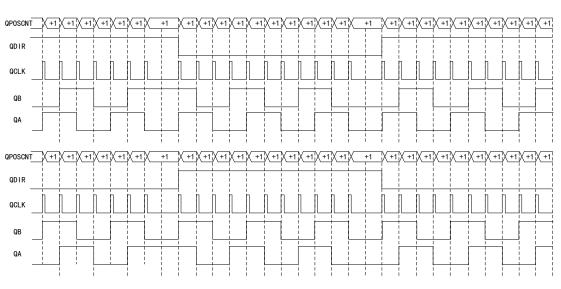

| 35.7  | Function description of quadrature coder unit (QDU)              | 674 |

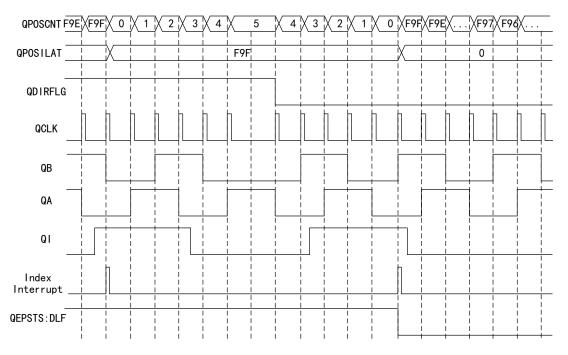

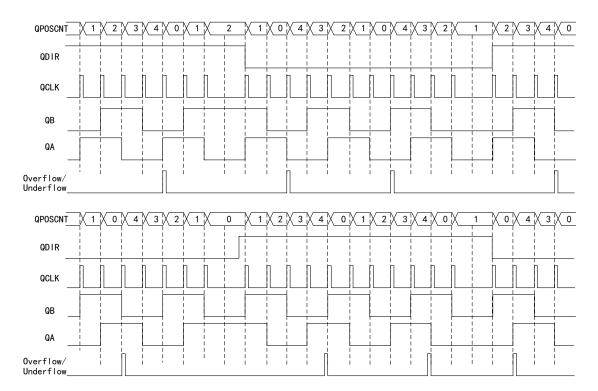

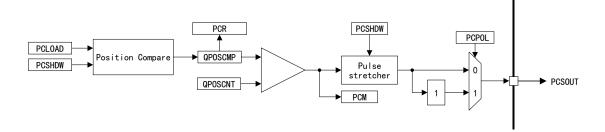

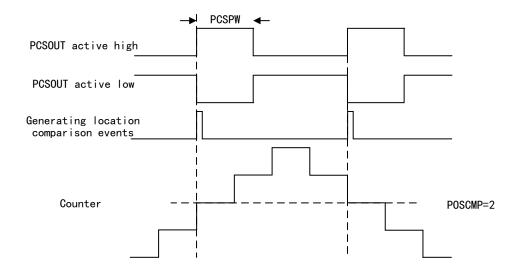

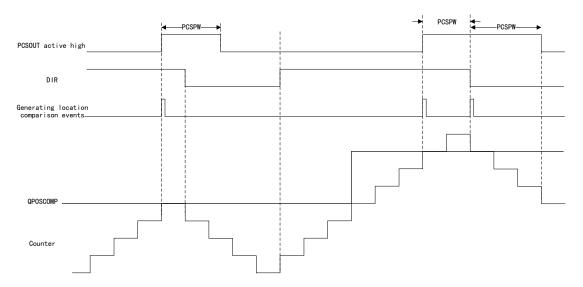

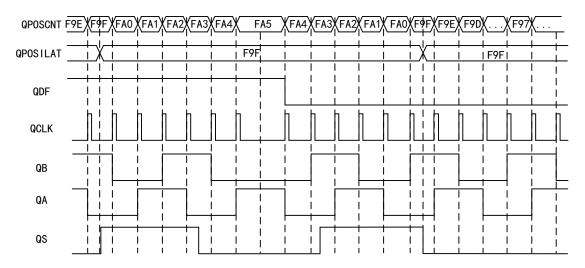

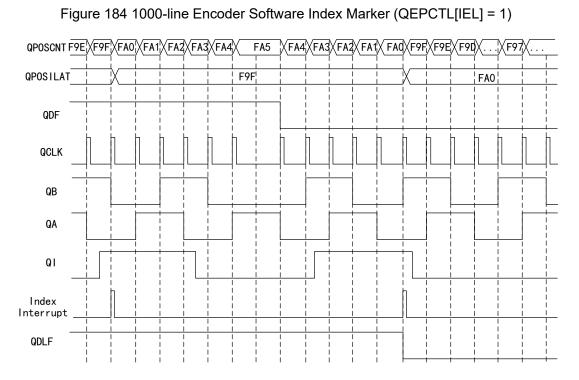

| 35.8  | Function description of position counter and control unit (PCCU) | 678 |

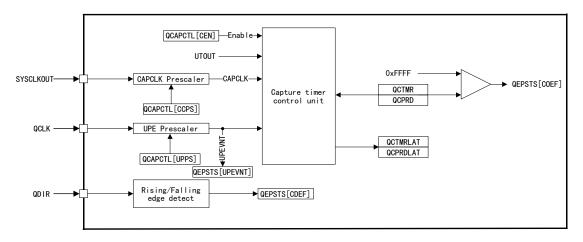

| 35.9  | Function description of edge capture unit                        | 684 |

| 35.10 | Register bank address                                            | 687 |

| 35.11 | Register address mapping                                         | 687 |

| 35.12 | Register functional description                                  | 688 |

| 36    | Serial peripheral interface (SPI)                                |     |

| 36.1  | Full Name and Abbreviation Description of Terms                  | 703 |

| 36.2  | Introduction                                                     |     |

| 36.3  | Main characteristics                                             | 703 |

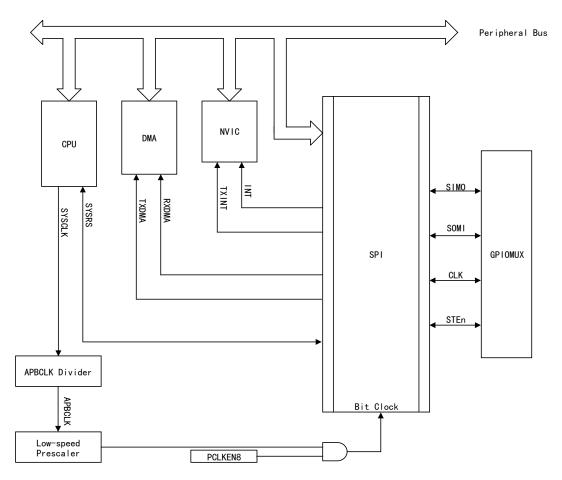

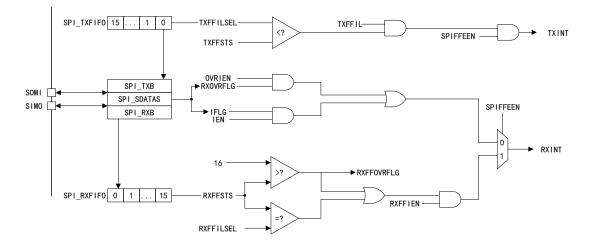

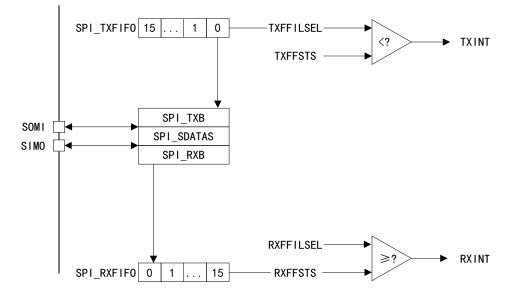

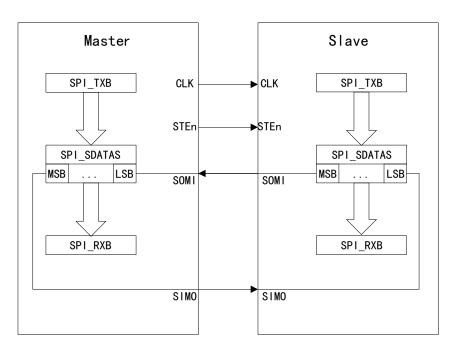

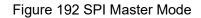

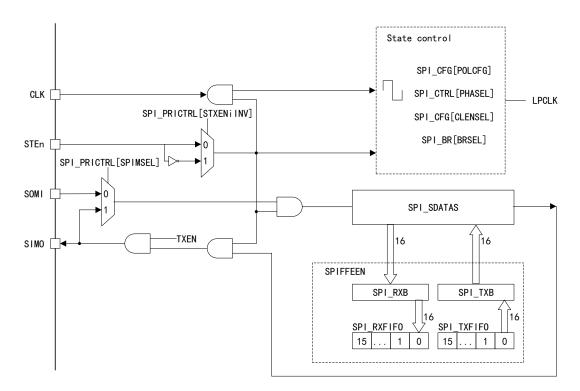

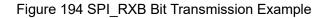

| 36.4  | Structure block diagram                                          | 704 |

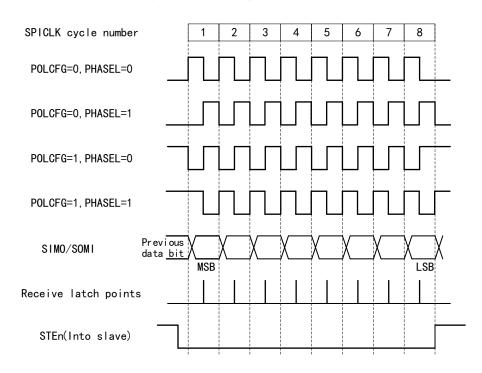

| 36.5  | Functional description                                           |     |

| 36.6 | Register bank address                              | 726 |

|------|----------------------------------------------------|-----|

| 36.7 | Register address mapping                           | 726 |

| 36.8 | Register functional description                    | 727 |

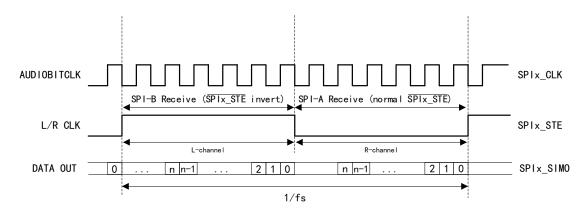

| 37   | Universal asynchronous receiver/transmitter (UART) | 738 |

| 37.1 | Full Name and Abbreviation Description of Terms    | 738 |

| 37.2 | Introduction                                       | 738 |

| 37.3 | Main characteristics                               | 738 |

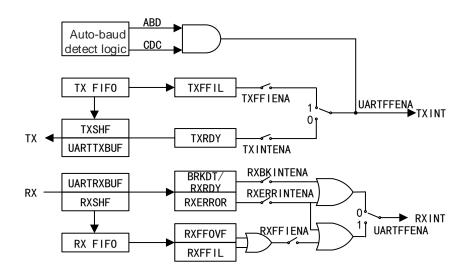

| 37.4 | Structure block diagram                            | 739 |

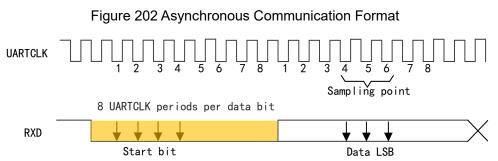

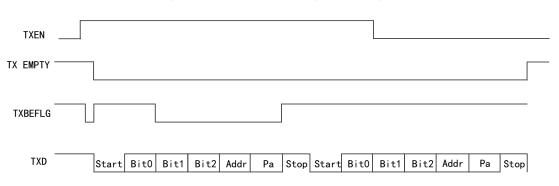

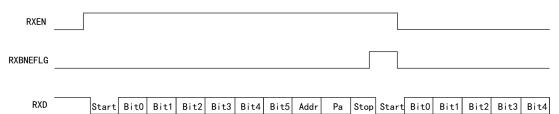

| 37.5 | Functional description                             | 739 |

| 37.6 | Register bank address                              | 748 |

| 37.7 | Register address mapping                           | 748 |

| 37.8 | Register functional description                    | 749 |

| 38   | Internal integrated circuit interface (I2C)        | 758 |

| 38.1 | Full Name and Abbreviation Description of Terms    | 758 |

| 38.2 | Introduction                                       | 758 |

| 38.3 | Main characteristics                               | 758 |

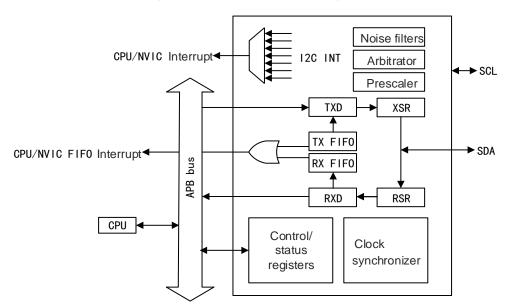

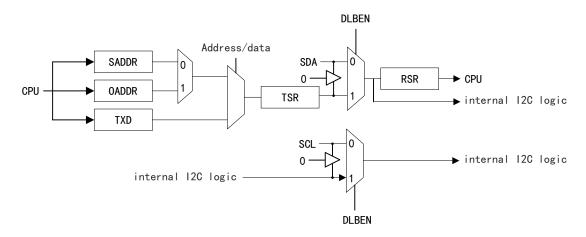

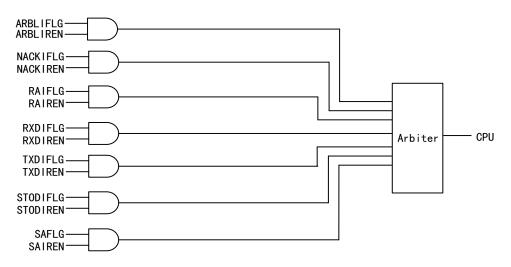

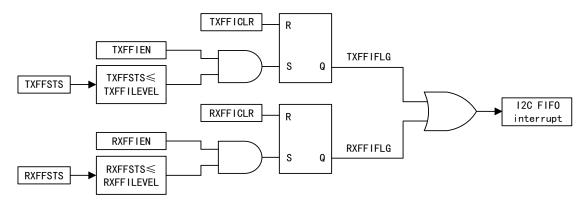

| 38.4 | Structure block diagram                            | 759 |

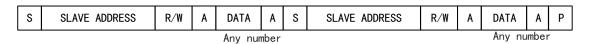

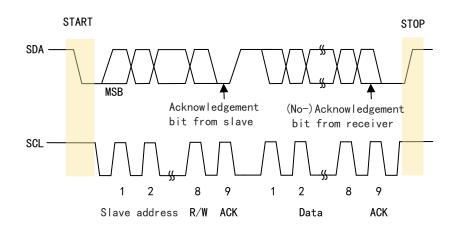

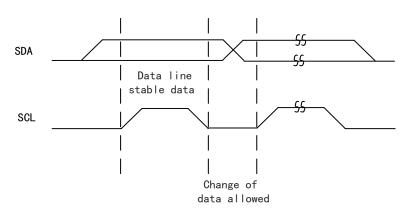

| 38.5 | Functional description                             | 759 |

| 38.6 | Register bank address                              | 770 |

| 38.7 | Register address mapping                           | 770 |

| 38.8 | Register functional description                    | 771 |

| 39   | Power management bus (PMBus)                       |     |

| 39.1 | Full Name and Abbreviation Description of Terms    | 782 |

| 39.2 | Introduction                                       | 782 |

| 39.3 | Main characteristics                               | 782 |

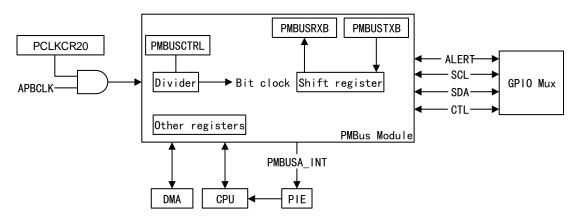

| 39.4 | Structure block diagram                            | 783 |

| 39.5 | Functional description                             | 783 |

| 39.6 | Register bank address                              | 805 |

| 39.7 | Register address mapping                           | 805 |

| 39.8 | Register functional description                    | 805 |

| 40   | Controller area network (CAN)                      | 817 |

| 40.1 | Full Name and Abbreviation Description of Terms    | 817 |

| 40.2 | Introduction                                       | 817 |

| 40.3 | Main characteristics                               | 817 |

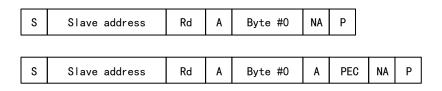

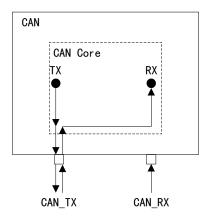

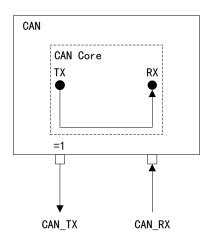

| 40.4 | Structure block diagram                            | 819 |

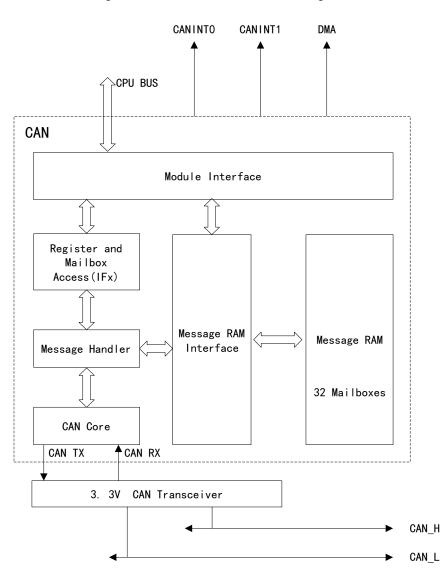

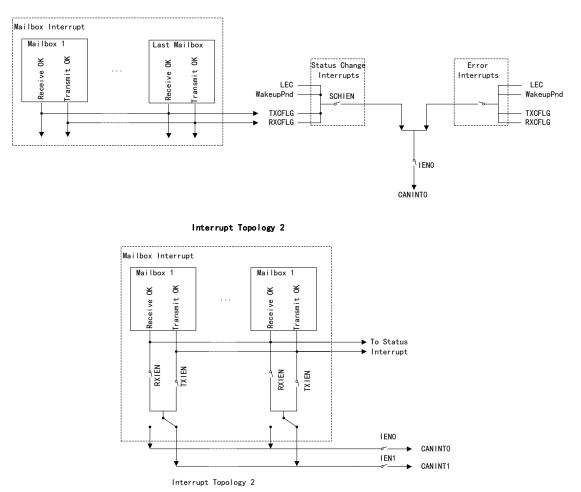

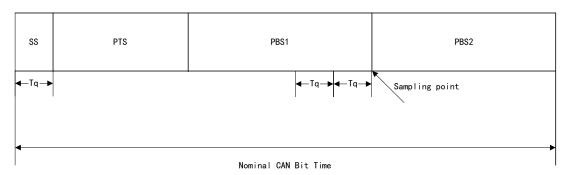

| 40.5 | Functional description                             | 820 |

| 40.6  | Register bank address                           | . 869 |

|-------|-------------------------------------------------|-------|

| 40.7  | Register address mapping                        | . 869 |

| 40.8  | Register functional description                 | . 870 |

| 41    | Local Interconnection Network (LIN)             | 899   |

| 41.1  | Full Name and Abbreviation Description of Terms | . 899 |

| 41.2  | Introduction                                    | . 899 |

| 41.3  | Main characteristics of UART                    | . 899 |

| 41.4  | Main characteristics of LIN                     | . 900 |

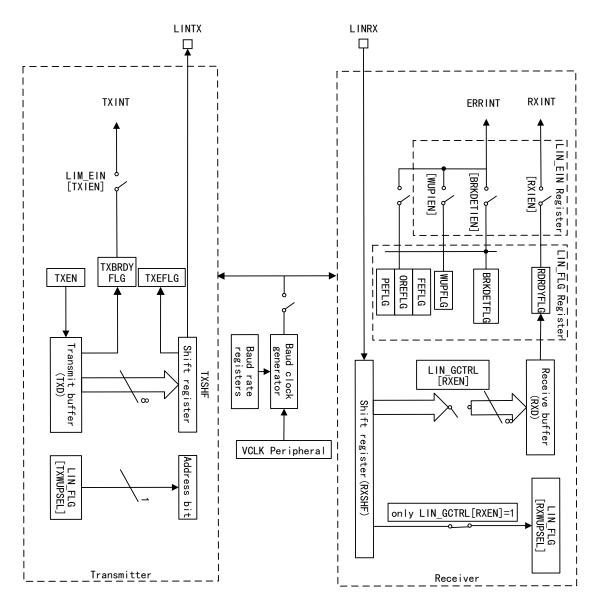

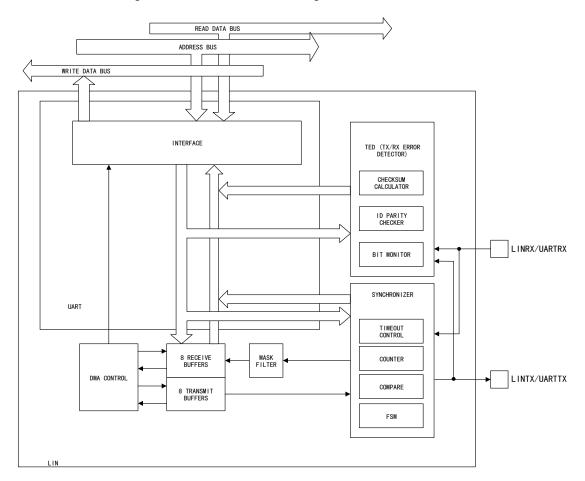

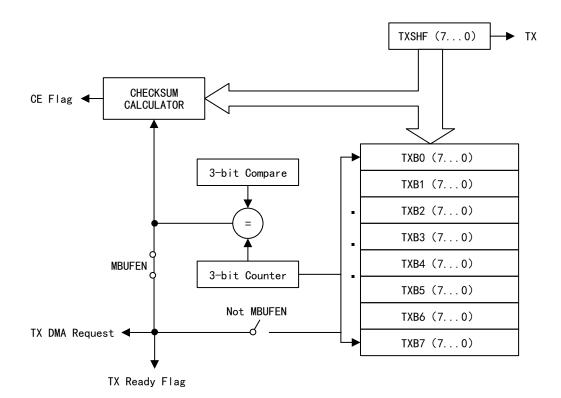

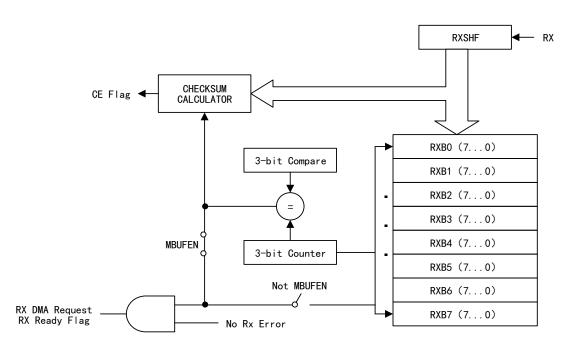

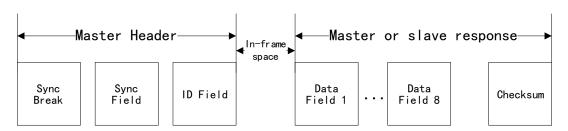

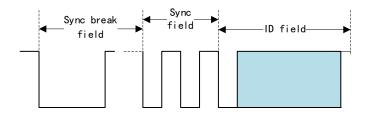

| 41.5  | Structure block diagram                         | . 901 |

| 41.6  | LIN Functional Description                      | . 904 |

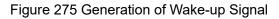

| 41.7  | Low-power mode                                  | . 928 |

| 41.8  | Simulation Mode                                 | . 931 |

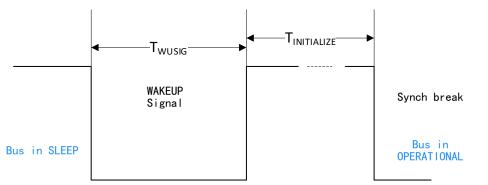

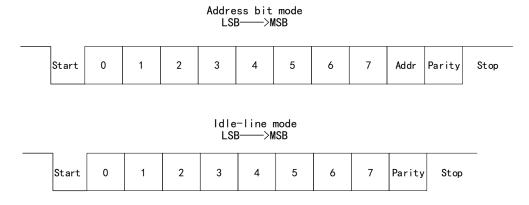

| 41.9  | UART Functional Description                     | . 931 |

| 41.10 | Register bank address                           | . 947 |

| 41.11 | Register address mapping                        | . 947 |

| 41.12 | Register functional description                 | . 948 |

| 42    | Quad serial peripheral interface (QSPI)         | 981   |

| 43    | Flexible logic block (FLB)                      | 982   |

| 44    | Revision history                                | 983   |

## **1** Introduction and document description rules

## 1.1 Introduction

G32R501x is a high-performance MCU developed by Geehy for real-time control applications. It is equipped with a Arm<sup>®</sup> Cortex<sup>®</sup>-M52 microprocessor based on the Arm v8.1-M architecture and supports up to 2 cores. The cores can work in parallel and collaborate efficiently, so it is suitable for such applications as motion control, photovoltaic inverters, digital power supplies, and on-board chargers (OBC).

The maximum operating frequency of G32R5xx MCU can be up to 250MHz, realizing custom datapath extension (CDE) for Arm Rv8-M. It is equipped with Helium<sup>™</sup> technology based on M-profile vector extension (MVE), which further improves the processing performance through innovative Zidian mathematical calculation extended instruction set. The Zidian mathematical calculation extended instruction set can quickly execute the algorithms that include the common trigonometric operations in transformation and torque loop calculation, and reduce the delay of common complex mathematical operation in coding application.

G32R501x supports up to 640KB Flash internally. The Flash is divided into two independent memory banks of 512KB and 128KB, supporting parallel programming and execution. Besides, through the built-in CFGSMS, efficient system partitioning can be implemented for 128KB SRAM storage on the chip. Each logical block has a size of 8KB, which can be configured for different types of usage, e.g. ITCM, DTCM, and SRAM. In addition, G32R501x also supports Flash ECC, RAM parity check, and security attribute configuration.

G32R501x chip integrates high-performance analog unit, which can further improve the system control performance. Three independent 12-bit ADC can accurately and efficiently collect and process multiple analog signals, thereby improving system throughput. 7 comparator subsystems can constantly monitor the input voltage level through the tripping function.

G32R501x includes performance-leading control peripherals (with frequencyindependent PWM and CAP/HRCAP), which can place excellent control over the system. The built-in 4-channel SDF is suitable for external isolated  $\Sigma$ - $\Delta$  modulators.

Universal communication ports (e.g. SPI, UART, I2C, LIN, and CAN) are built in G32R501x, and multiple multiplexing options are provided to meet the communication requirements of various applications. The G32R501x device also provides the PMBus interface and high-speed QSPI interface that fully comply with the standards. Besides, G32R501x also supports JTAG, cJTAG, and SWD debugging interfaces. The multiple debugging modes are suitable for different system environments and performance requirements.

G32R501x supports the operating temperatures ranging from -40°C to 105°C/125°C, and provides multiple packages for choice such as QFN56, LQFP64, LQFP80, and LQFP100.

#### 1.1.1 Register access method

If the registers described in the Manual are 16-bit registers, these registers can be accessed according to 16-bit operations only; if the registers described in the Manual are 32-bit registers, they can only be accessed according to 32-bit operations. CPU cannot initiate non-aligned access to the peripheral area; otherwise, it will enter hardfault.

## **1.2** Document description rules

#### 1.2.1 Register read/write mode

| R/W Description         |                                                                                                                        | Abbreviations |

|-------------------------|------------------------------------------------------------------------------------------------------------------------|---------------|

| read/write              | read/write The software can read and write this bit.                                                                   |               |

| read-only               | The software can only read this bit.                                                                                   | R             |

| write-only              | The software can only write this bit, and after reading this bit, the reset value will be returned.                    | W             |

| read/clear              | The software can read this bit and clear it by writing 1. Writing 0 has no effect on this bit.                         | RC_W1         |

| read/clear              | The software can read this bit and clear it by writing 0. Writing 1 has no effect on this bit.                         | RC_W0         |

| read/clear by read      | The software can read this bit, reading this bit will automatically clear<br>it to 0, and writing this bit is invalid. | RC_R          |

| read/set                | The software can read and set this bit, and writing 0 has no effect on this bit.                                       | R/S           |

| read-only write trigger | The software can read this bit and writing 0 or 1 can trigger an event but has no effect on the value of this bit.     | RT_W          |

| toggle                  | The software can flip this bit only by writing 1, and writing 0 has no effect on this bit.                             | т             |

| Read Returns 0s         | Read returns 0                                                                                                         | R-0           |

| Write 1 to set          | Write 1 to set                                                                                                         | W1S           |

| Write 1 to clear        | Write 1 to clear                                                                                                       | W1C           |

| Write once              | Write once                                                                                                             | WOnce         |

| Write Set once          | Write set once                                                                                                         | WSonce        |

| Write once              | Write this bit once                                                                                                    | WO            |

Table 1 R/W Abbreviation and Description

## 1.2.2 Full Name and Abbreviation Description of Terms

| Full name in Chinese                                          | Full name in English                                       | English abbreviation |

|---------------------------------------------------------------|------------------------------------------------------------|----------------------|

| Reset and Clock<br>Management                                 | Reset and Clock Management                                 | RCM                  |

| Clock Recovery System                                         | Clock Recovery System                                      | CRS                  |

| Power management unit                                         | Power Management Unit                                      | PMU                  |

| Nested Vector Interrupt<br>Controller                         | Nested Vector Interrupt Controller                         | NVIC                 |

| External Interrupt/Event<br>Controller                        | External Interrupt /Event Controller                       | EXTI                 |

| Direct Memory Access                                          | Direct Memory Access                                       | DMA                  |

| Debug MCU                                                     | Debug MCU                                                  | DBG MCU              |

| General-Purpose<br>Input/Output Pin                           | General-Purpose Input Output Pin                           | GPIO                 |

| Alternate Function<br>Input/Output Pin                        | Alternate Function Input Output Pin                        | AFIO                 |

| Timer                                                         | Timer                                                      | TMR                  |

| Watchdog Timer                                                | Watchdog Timer                                             | WDT                  |

| Independent watchdog                                          | Independent Watchdog Timer                                 | IWDT                 |

| Window watchdog                                               | Windows Watchdog Timer                                     | WWDT                 |

| Real-time Clock                                               | Real-Time Clock                                            | RTC                  |

| Universal<br>Synchronous/Asynchronous<br>Receiver Transmitter | Universal Synchronous Asynchronous Receiver<br>Transmitter | UART                 |

| Inter-integrated circuit<br>interface                         | Inter-integrated Circuit Interface                         | 12C                  |

| Serial Peripheral Interface                                   | Serial Peripheral Interface                                | SPI                  |

| Inter-IC Sound Interface                                      | Inter-IC Sound Interface                                   | 12S                  |

| Controller LAN                                                | Controller Area Network                                    | CAN                  |

| Analog-to-digital converter                                   | Analog-to-Digital Converter                                | ADC                  |

| Digital-to-analog converter                                   | Digital-to-Analog Converter                                | DAC                  |

| Comparator                                                    | Comparator                                                 | COMP                 |

| Cyclic Redundancy Check<br>Calculation Unit                   | Cyclic Redundancy Check Calculation Unit                   | CRC                  |

#### Table 2 Full Name and Abbreviation of Modules

# 2 CPU and system architecture

## 2.1 Full Name and Abbreviation Description of Terms

| Full name in English                                                      | English abbreviation |

|---------------------------------------------------------------------------|----------------------|

| Configurable Static Memory Subsystem                                      | CFGSMS               |

| Software                                                                  | SW                   |

| Hardware                                                                  | HW                   |

| Interface                                                                 | IF                   |

| AHB slave interface                                                       | ahbs_if              |

| Hardware-oriented, pre-synthesis user-defined                             | -                    |

| Store queue                                                               | STQ                  |

| Built-in self test                                                        | BIST                 |

| The number of all slaves (include ITCM/DTCM/AHB). The default value is 7. | IF_NUM               |

| The width of the key. The default value is 8.                             | KEY_DW               |

| The width of the low power counter. The default value is 8.               | CNT_WID              |

| The number of the ITCM. The default value is 2.                           | ITCM_NUM             |

| The number of the DTCM. The default value is 2.                           | DTCM_NUM             |

| Logic Bank                                                                | Bank                 |

Table 3 Full Name and Abbreviation Description of Terms

## 2.2 Introduction

R501 SoC is a system on a chip (SoC) based on Arm<sup>®</sup> Cortex<sup>®</sup>-M52 dual cores. This SoC adopts the widely used AMBA 2.0 bus to integrate peripheral IP components: the components that require broad bandwidth are connected to the AMBA AHB bus, while the low-speed components are connected to the AMBA APB bus. DMA cannot access the registers related to FLB.

## 2.3 Main characteristics

#### **Computation part**

- (1) CPU0

- Arm<sup>®</sup> Cortex<sup>®</sup>-M52

- Cache: Support 4KB cache

- TCM interface: It supports 36-bit wide 16KB (default size) ITCM, 36-bit wide 8KB (default size) DTCM0, and 36-bit wide 8KB (default size) DTCM1, all of which can be configured through CFGSMS. Support parity check function.

- Support FPU/CDE/COP

- (2) CPU1

- Arm<sup>®</sup> Cortex<sup>®</sup>-M52

- Cache: Support 4KB cache

- TCM interface: It supports 36-bit wide 16KB (default size) ITCM, 36-bit wide 8KB (default size) DTCM0, and 36-bit wide 8KB (default size) DTCM1, all of which can be configured through CFGSMS. Support parity check function.

- FPU/CDE/COP

#### Storage part

- (1) On-chip SRAM1

- 36 bits wide, 32KB (default size), configurable through CFGSMS

- Support parity check

- (2) On-chip SRAM2

- 36 bits wide, 16KB (default size), configurable through CFGSMS

- Support parity check

- (3) On-chip SRAM3

- 36 bits wide, 32KB (default size), configurable through CFGSMS

- Support parity check

- (4) On-chip FLASH

- 144 bits wide

- The total capacity is 640KB (512KB+128KB)

- Support switching between single/dual banks

- (5) On-chip Boot ROM

- 32 bits wide, 128KB

- (6) On-chip Secure ROM

- 32 bits wide, 64KB

- (7) On-chip CAN-dedicated SRAM

- 1KB (CANA) + 1KB (CANB)

#### **Bus architecture**

- (1) AHB bus

- 32 bits wide

- 7 masters: CPU0-C-BUS, CPU0-S-BUS, CPU0-P-BUS, CPU1-C-BUS, CPU1-S-BUS, CPU1-P-BUS, DMA

- 15 slaves: CPU0-AHBT, CPU1-AHBT, SRAM1, SRAM2, SRAM3, FLASH1, FLASH2, Boot ROM, Secure ROM, DEMUX0, DEMUX1, DEMUX2, APB0, APB1, APB2.

- (2) DEMUX0

- 4 slaves: GPIOCTRL, CPIODATA, INPUT\_XBAR, XBAR

- (3) DEMUX1

- 9 slaves: NVMC, CFGSMS, SYSC, DCS, QSPI, ANALOG SUBSYSTEM, WDT, NMIWDT, APB3

- (4) DEMUX2

- 6 slaves: CPUTIM0~2, DMA, EXTI, APB4

- (5) APB0

- 16 slaves: PWM1~8, CAP1~7, SDFM

- (6) APB1

- 9 slaves: COMP1~7, QEP1, QEP2

- (7) APB2

- 3 slaves: ADCA, ADCB, ADCC

- (8) APB3

- 7 slaves: LIN, UARTA, SPIA, CANA, I2C, DACA, DACB

- (9) APB4

- 9 slaves: UARTB, SPIB, CANB, PMBUS, DCCOPM, FLB1~4

#### **Clocks and Reset**

- (1) Clock

- Internal clock source: INTOSC1 (10MHz), INTOSC2 (10MHz), PLL (250MHz)

- External clock source: XTAL (2~20MHz)

- (2) Reset source

- On-chip power-on reset (POR)

- External reset (XRS)

- Debugger reset (SYSRS)

- Watchdog reset (WDRS)

- NMI watchdog reset (NMIWDRS)

- DCS Safe Code Copy Reset (SCCRESET)

Characteristics of physical layer

- (1) Supply voltage: 3.3V/1.1V

- (2) Frequency

- The maximum frequency of SYSCLK is 250MHz

- The maximum clock frequency of low-speed peripherals is 125MHz

- (3) Byte order: Little-endian mode

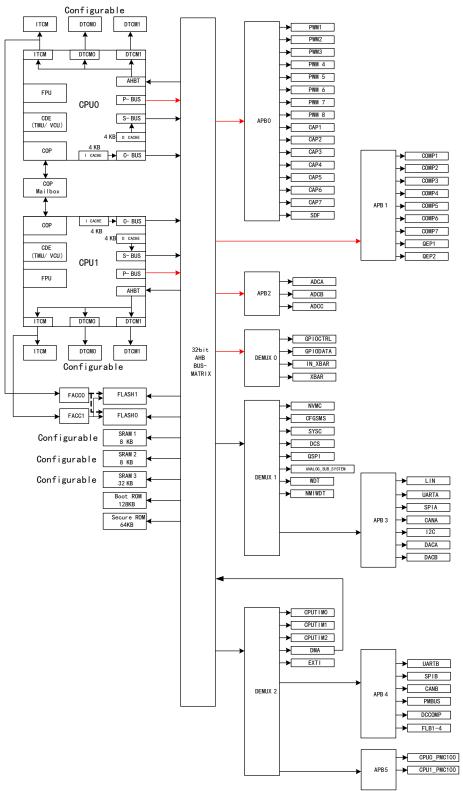

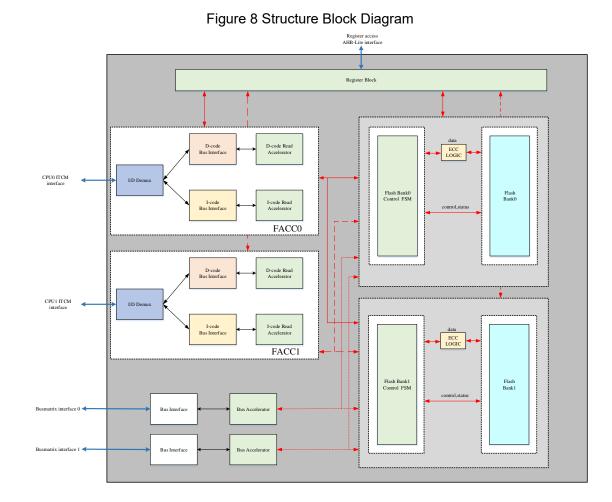

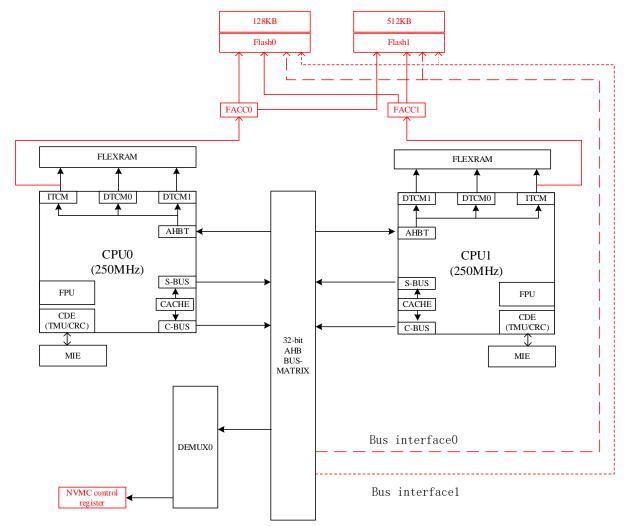

## 2.4 Structure block diagram

Figure 1 CPU Architecture

Note:

- (1) The red lines in the figure represent bus bridge.

- (2) The size of ITCM/DTCM/SRAM is configured using CFGSMS.

# 2.5 Functional description

## 2.5.1 Memory address mapping

#### Table 4 General-purpose Memory Mapping

|                         | Size (maximum                                |                                                             |

|-------------------------|----------------------------------------------|-------------------------------------------------------------|

| Address range           | value)                                       | Description                                                 |

| 0x0000 0000-0x0001 FFFF | 128KB                                        | CPU0 ITCM (64KB for single-core version, and 48KB for       |

|                         | IZOND                                        | dual-core version by default)                               |

|                         |                                              | CPU0 ITCM (CPU0-AHBT)                                       |

| 0xA000 0000-0xA001 FFFF | 128KB                                        | (64KB for single-core version, and 48KB for dual-core       |

|                         |                                              | version by default)                                         |

| 0x0000 0000-0x0001 FFFF | 128KB                                        | CPU1 ITCM (0KB for single-core version, and 8KB for dual-   |

|                         | 12010                                        | core version by default)                                    |

|                         |                                              | CPU1 ITCM (CPU1-AHBT)                                       |

| 0xA100 0000-0xA101 FFFF | 128KB                                        | (0KB for single-core version, and 8KB for dual-core version |

|                         |                                              | by default)                                                 |

| 0x0008 0000-0x0008 BFFF | 48KB                                         | FLASH INFO on ITCM                                          |

| 0x0009 0000-0x0009 3FFF | 09 0000-0x0009 3FFF 16KB FLASH INFO1 on ITCM |                                                             |

| 0x0010 0000-0x0019 FFFF | 640KB                                        | FLASH memory on ITCM                                        |

| 0x0800 0000-0x0809 FFFF | 640KB                                        | FLASH memory on BUSMATRIX                                   |

| 0x0810 0000-0x0810 BFFF | 48KB                                         | FLASH INFO on BUSMATRIX                                     |

| 0x0818 0000-0x0818 3FFF | 16KB                                         | FLASH INFO1 on BUSMATRIX                                    |

| 0x0900 0000-0x0901 FFFF | 128KB                                        | FLASH ECC                                                   |

| 0x1000-0000-0x1001 FFFF | 128KB                                        | Boot ROM                                                    |

| 0x1002 0000-0x1002 FFFF | 64KB                                         | Secure ROM                                                  |

| 0x2000 0000-0x2001 FFFF | 128KB                                        | CPU0 DTCM (16KB for single-core version, and 16KB for       |

| 0x2000 0000-0x2001 FFFF | IZOND                                        | dual-core version by default)                               |

|                         |                                              | CPU0 DTCM (CPU0-AHBT)                                       |

| 0xA010 0000-0xA011 FFFF | 128KB                                        | (16KB for single-core version, and 16KB for dual-core       |

|                         |                                              | version by default)                                         |

| 0x2000 0000-0x2001 FFFF | 128KB                                        | CPU1 DTCM (0KB for single-core version, and 8KB for dual-   |

|                         | 12010                                        | core version by default)                                    |

| Address range           | Size (maximum<br>value) | Description                                                 |

|-------------------------|-------------------------|-------------------------------------------------------------|

|                         |                         | CPU1 DTCM (CPU1-AHBT)                                       |

| 0xA110 0000-0xA111 FFFF | 128KB                   | (0KB for single-core version, and 8KB for dual-core version |

|                         |                         | by default)                                                 |

| 0x2010 0000-0x2011 FFFF | 128KB                   | SRAM1 (Default 8KB)                                         |

| 0x2020 0000-0x2021 FFFF | 128KB                   | SRAM2 (Default 8KB)                                         |

| 0x2030 0000-0x2031 FFFF | 128KB                   | SRAM3 (Default 32KB)                                        |

#### Table 5 Universal Bus Address Mapping

| Address range           | Bus    | Function       |

|-------------------------|--------|----------------|

| 0x4000 0000-0x4000 FFFF | APB0   | APB peripheral |

| 0x4001 0000-0x4001 FFFF | APB1   | APB peripheral |

| 0x4002 0000-0x4002 FFFF | APB2   | APB peripheral |

| 0x4003 0000-0x4003 FFFF | DEMUX0 | AHB peripheral |

| 0x5000 0000-0x5000 FFFF | APB3   | APB peripheral |

| 0x5000 0000-0x5002 FFFF | DEMUX1 | AHB peripheral |

| 0x6000 0000-0x6FFF FFFF | DEMOXI |                |

| 0x5010 0000-0x5010 3FFF | APB4   | APB peripheral |

| 0x5010 4000-0x5010 FFFF | APB5   | APB peripheral |

| 0x5010 0000-0x5011 FFFF | DEMUX2 | AHB peripheral |

#### 2.5.2 Peripheral address mapping

The register addresses of the register blocks of most on-chip peripherals are allocated in units of 1KB. For the modules that require extra address space, an extra 1KB block is allocated. Within a 1KB block, peripheral registers may not be fully decoded. The description of each peripheral will define the access results of the undecoded registers. It returns zero when reading reserved bits from a 32-bit register, and has no effect on write to the reserved bits. Generally speaking, to ensure compatibility with future products, the unimplemented bits should return zero.

| Bus  | IP   | Address                 |

|------|------|-------------------------|

|      | PWM1 | 0x4000 0000-0x4000 03FF |

| APB0 | PWM2 | 0x4000 0400-0x4000 07FF |

|      | PWM3 | 0x4000 0800-0x4000 0BFF |

|      | PWM4 | 0x4000 0C00-0x4000 0FFF |

#### Table 6 Peripheral Address Mapping

| Bus    | IP         | Address                 |

|--------|------------|-------------------------|

|        | PWM5       | 0x4000 1000-0x4000 13FF |

|        | PWM6       | 0x4000 1400-0x4000 17FF |

|        | PWM7       | 0x4000 1800-0x4000 1BFF |

|        | PWM8       | 0x4000 1C00-0x4000 1FFF |

|        | CAP1       | 0x4000 2000-0x4000 23FF |

|        | CAP2       | 0x4000 2400-0x4000 27FF |

|        | CAP3       | 0x4000 2800-0x4000 2BFF |

|        | CAP4       | 0x4000 2C00-0x4000 2FFF |

|        | CAP5       | 0x4000 3000-0x4000 33FF |

|        | CAP6       | 0x4000 3400-0x4000 37FF |

|        | CAP7       | 0x4000 3800-0x4000 3BFF |

|        | SDF        | 0x4000 3C00-0x4000 3FFF |

|        | Reserved   | 0x4000 4000-0x4000 FFFF |

|        | COMP1      | 0x4001 1C00-0x4001 1FFF |

|        | COMP2      | 0x4001 2000-0x4001 23FF |

|        | COMP3      | 0x4001 2400-0x4001 27FF |

|        | COMP4      | 0x4001 2800-0x4001 2BFF |

|        | COMP5      | 0x4001 2C00-0x4001 2FFF |

| APB1   | COMP6      | 0x4001 3000-0x4001 33FF |

|        | COMP7      | 0x4001 3400-0x4001 37FF |

|        | QEP1       | 0x4001 3800-0x4001 3BFF |

|        | QEP2       | 0x4001 3C00-0x4001 3FFF |

|        | Reserved   | 0x4001 4000-0x4001 FFFF |

|        | ADCA       | 0x4002 0000-0x4002 03FF |

|        | ADCB       | 0x4002 0400-0x4002 07FF |

| APB2   | ADCC       | 0x4002 0800-0x4002 0BFF |

|        | Reserved   | 0x4002 0C00-0x4002 FFFF |

|        | GPIOCTRL   | 0x4003 0000-0x4003 07FF |

| DEMUX0 | GPIODATA   | 0x4003 0800-0x4003 0BFF |

| DEMORO | INPUTXBAR  | 0x4003 0C00-0x4003 0C7F |

|        | SyncSocREG | 0x4003 0C80-0x4003 0FFF |

| Bus    | IP                | Address                 |

|--------|-------------------|-------------------------|

|        | XBAR_REG          | 0x4003 1000-0x4003 103F |

|        | PWM_XBAR_REG      | 0x4003 11C0-0x4003 123F |

|        | FLB_XBAR_REG      | 0x4003 1240-0x4003 12BF |

|        | OUTPUT_XBAR_REG   | 0x4003 12C0-0x4003 133F |

|        | Reserved          | 0x4003 1400-0x4003 FFFF |

|        | LIN               | 0x5000 0000-0x5000 03FF |

|        | Reserved          | 0x5000 0400-0x5000 0BFF |

|        | UARTA             | 0x5000 0C00-0x5000 0FFF |

|        | SPIA              | 0x5000 1000-0x5000 13FF |

| APB3   | I2C               | 0x5000 1400-0x5000 17FF |

|        | DACA              | 0x5000 1800-0x5000 1BFF |

|        | DACB              | 0x5000 1C00-0x5000 1FFF |

|        | CANA              | 0x5000 2000-0x5000 27FF |

|        | Reserved          | 0x5000 2800-0x5000 FFFF |

|        | APB3              | 0x5000 0000-0x5000 FFFF |

|        | NVMC              | 0x5001 0000-0x5001 07FF |

|        | CFGSMS            | 0x5001 0800-0x5001 0BFF |

|        | Reserved          | 0x5001 0C00-0x5001 FFFF |

|        | SYSC              | 0x5002 0000-0x5002 3FFF |

|        | DCS               | 0x5002 4000-0x5002 5FFF |

| DEMUX1 | QSPI              | 0x5002 6000-0x5002 63FF |

|        | WWDT              | 0x5002 6400-0x5002 64BF |

|        | NMIWDT            | 0x5002 64C0-0x5002 67FF |

|        | Reserved          | 0x5002 6800-0x5002 7FFF |

|        | ANALOG_SUB_SYSTEM | 0x5002 8000-0x5002 83FF |

|        | Reserved          | 0x5002 8400-0x5002 FFFF |

|        | QSPI_MEMORY       | 0x6000 0000-0x6FFF FFFF |

|        | UARTB             | 0x5010 0000-0x5010 03FF |

|        | SPIB              | 0x5010 0400-0x5010 07FF |

| APB4   | PMBUS             | 0x5010 0800-0x5010 0BFF |

|        | Reserved          | 0x5010 0C00-0x5010 0FFF |

|        | Reserved          | 0x5010 1000-0x5010 13FF |

| Bus    | IP          | Address                 |

|--------|-------------|-------------------------|

|        | DCCOMP      | 0x5010 1400-0x5010 17FF |

|        | CANB        | 0x5010 1800-0x5010 1FFF |

|        | FLB1        | 0x5010 2000-0x5010 27FF |

|        | FLB2        | 0x5010 2800-0x5010 2FFF |

|        | FLB3        | 0x5010 3000-0x5010 37FF |

|        | FLB4        | 0x5010 3800-0x5010 3FFF |

|        | CPU0_PMC100 | 0x5010 4000-0x5010 4FFF |

| APB5   | CPU1_PMC100 | 0x5010 5000-0x5010 5FFF |

|        | Reserved    | 0x5010 6000-0x5010 FFFF |

|        | APB4        | 0x5010 0000-0x5010 3FFF |

|        | APB5        | 0x5010 4000-0x5010 FFFF |

|        | CPUTIM0     | 0x5011 0000-0x5011 03FF |

| DEMUX2 | CPUTIM1     | 0x5011 0400-0x5011 07FF |

| DEMOX2 | CPUTIM2     | 0x5011 0800-0x5011 0BFF |

|        | DMA         | 0x5011 0C00-0x5011 0FFF |

|        | EXTI        | 0x5011 1000-0x5011 13FF |

|        | Reserved    | 0x5011 1400-0x5011 FFFF |

#### 2.5.3 Bus matrix

|                | Table 7 Bus Matrix Interconnection |               |               |                             |               |               |              |

|----------------|------------------------------------|---------------|---------------|-----------------------------|---------------|---------------|--------------|

| Bus slave      | CPU0<br>C-BUS                      | CPU0<br>S-BUS | CPU0<br>P-BUS | Bus master<br>CPU1<br>C-BUS | CPU1<br>S-BUS | CPU1<br>P-BUS | DMA          |

| CPU0-AHBT      | $\times$                           | ×             | ×             | ×                           | $\checkmark$  | ×             | $\checkmark$ |

| CPU1-AHBT      | $\times$                           | $\checkmark$  | $\times$      | ×                           | ×             | $\times$      |              |

| FLASH<br>BANK0 | $\checkmark$                       | ×             | ×             | $\checkmark$                | ×             | ×             |              |

| FLASH<br>BANK1 | $\checkmark$                       | ×             | ×             | $\checkmark$                | ×             | ×             |              |

| Boot ROM       | $\checkmark$                       | ×             | ×             | $\checkmark$                | ×             | ×             | $\checkmark$ |

| Secure ROM     |                                    | $\times$      | $\times$      | $\checkmark$                | $\times$      | $\times$      |              |

| SRAM1          | $\times$                           | $\checkmark$  | $\times$      | $\times$                    | $\checkmark$  | $\times$      | $\checkmark$ |

| SRAM2          | $\times$                           | $\checkmark$  | $\times$      | $\times$                    | $\checkmark$  | $\times$      | $\checkmark$ |

| SRAM3          | $\times$                           | $\checkmark$  | $\times$      | $\times$                    | $\checkmark$  | $\times$      |              |

| DEMUX0 | $\times$ | $\times$     | $\checkmark$ | $\times$ | $\times$     | $\checkmark$ | $\checkmark$ |

|--------|----------|--------------|--------------|----------|--------------|--------------|--------------|

| DEMUX1 | $\times$ | $\checkmark$ | $\times$     | $\times$ | $\checkmark$ | $\times$     | $\checkmark$ |

| DEMUX2 | $\times$ | $\checkmark$ | $\times$     | $\times$ | $\checkmark$ | $\times$     | $\checkmark$ |

| APB0   | $\times$ | $\times$     | $\checkmark$ | $\times$ | $\times$     | $\checkmark$ | $\checkmark$ |

| APB1   | ×        | $\times$     | $\checkmark$ | ×        | ×            | $\checkmark$ | $\checkmark$ |

| APB2   | ×        | $\times$     | $\checkmark$ | ×        | ×            | $\checkmark$ | $\checkmark$ |

## 2.5.4 Interrupt

#### Table 8 Interrupt Vector Table

| Vector ID | Name                  |

|-----------|-----------------------|

| 0         | Reserved              |

| 1         | Reserved              |

| 2         | Reserved              |

| 3         | Reserved              |

| 4         | Reserved              |

| 5         | Reserved              |

| 6         | Reserved              |

| 7         | Reserved              |

| 8         | Reserved              |

| 9         | Reserved              |

| 10        | Reserved              |

| 11        | DCCOMP interrupt      |

| 12        | Reserved              |

| 13        | TMR1 Interrupt        |

| 14        | TMR2 Interrupt        |

| 15        | Reserved              |

| 16        | TAOSMS Interrupt      |

| 17        | cop_te_irq_to_cpu0[0] |

| 18        | cop_te_irq_to_cpu0[1] |

| 19        | cop_te_irq_to_cpu0[2] |

| 20        | cop_te_irq_to_cpu0[3] |

| 21        | cop_rf_irq_to_cpu0[0] |

| 22        | cop_rf_irq_to_cpu0[1] |

| Vector ID | Name                     |  |

|-----------|--------------------------|--|

| 23        | cop_rf_irq_to_cpu0[2]    |  |

| 24        | cop_rf_irq_to_cpu0[3]    |  |

| 25        | cop_gp_irq_to_cpu0[0]    |  |

| 26        | cop_gp_irq_to_cpu0[1]    |  |

| 27        | cop_gp_irq_to_cpu0[2]    |  |

| 28        | cop_gp_irq_to_cpu0[3]    |  |

| 29        | Reserved                 |  |

| 30        | Reserved                 |  |

| 31        | Reserved                 |  |

| 32        | ADCA1 interrupt          |  |

| 33        | ADCB1 interrupt          |  |

| 34        | ADCC1 interrupt          |  |

| 35        | Reserved                 |  |

| 36        | Reserved                 |  |

| 37        | Reserved                 |  |

| 38        | TMR0 interrupt           |  |

| 39        | WAKEUP interrupt         |  |

| 40        | PWM1 trip zone interrupt |  |

| 41        | PWM2 trip zone interrupt |  |

| 42        | PWM3 trip zone interrupt |  |

| 43        | PWM4 trip zone interrupt |  |

| 44        | PWM5 trip zone interrupt |  |

| 45        | PWM6 trip zone interrupt |  |

| 46        | PWM7 trip zone interrupt |  |

| 47        | PWM8 trip zone interrupt |  |

| 48        | PWM1 interrupt           |  |

| 49        | PWM2 interrupt           |  |

| 50        | PWM3 interrupt           |  |

| 51        | PWM4 interrupt           |  |

| 52        | PWM5 interrupt           |  |

| 53        | PWM6 interrupt           |  |

| Vector ID | Name              |

|-----------|-------------------|

| 54        | PWM7 interrupt    |

| 55        | PWM8 interrupt    |

| 56        | CAP1 interrupt    |

| 57        | CAP2 interrupt    |

| 58        | CAP3 interrupt    |

| 59        | CAP4 interrupt    |

| 60        | CAP5 interrupt    |

| 61        | CAP6 interrupt    |

| 62        | CAP7 interrupt    |

| 63        | Reserved          |

| 64        | QEP1 interrupt    |

| 65        | QEP2 interrupt    |

| 66        | Reserved          |

| 67        | Reserved          |

| 68        | FLB1 interrupt    |

| 69        | FLB2 interrupt    |

| 70        | FLB3 interrupt    |

| 71        | FLB4 interrupt    |

| 72        | SPIA_RX interrupt |

| 73        | SPIA_TX interrupt |

| 74        | SPIB_RX interrupt |

| 75        | SPIB_TX interrupt |

| 76        | Reserved          |

| 77        | Reserved          |

| 78        | Reserved          |

| 79        | Reserved          |

| 80        | DMA_CH1 interrupt |

| 81        | DMA_CH2 interrupt |

| 82        | DMA_CH3 interrupt |

| 83        | DMA_CH4 interrupt |

| 84        | DMA_CH5 interrupt |

| Vector ID | Name                 |

|-----------|----------------------|

| 85        | DMA_CH6 interrupt    |

| 86        | Reserved             |

| 87        | Reserved             |

| 88        | I2CA interrupt       |

| 89        | I2CA FIFO interrupt  |

| 90        | QSPI interrupt       |

| 91        | Reserved             |

| 92        | Reserved             |

| 93        | Reserved             |

| 94        | Reserved             |

| 95        | Reserved             |

| 96        | UARTA RX interrupt   |

| 97        | UARTA TX interrupt   |

| 98        | UARTB RX interrupt   |

| 99        | UARTB TX interrupt   |

| 100       | CANA interrupt 0     |

| 101       | CANA interrupt 1     |

| 102       | CANB interrupt 0     |

| 103       | CANB interrupt 1     |

| 104       | ADCA event interrupt |

| 105       | ADCA2 interrupt      |

| 106       | ADCA3 interrupt      |

| 107       | ADCA4 interrupt      |

| 108       | ADCB event interrupt |

| 109       | ADCB2 interrupt      |

| 110       | ADCB3 interrupt      |

| 111       | ADCB4 interrupt      |

| 112       | exti_line0 interrupt |

| 113       | exti_line1 interrupt |

| 114       | exti_line2 interrupt |

| 115       | exti_line3 interrupt |

| Vector ID | Name                  |

|-----------|-----------------------|

| 116       | exti_line4 interrupt  |

| 117       | exti_line5 interrupt  |

| 118       | exti_line6 interrupt  |

| 119       | exti_line7 interrupt  |

| 120       | exti_line8 interrupt  |

| 121       | exti_line9 interrupt  |

| 122       | exti_line10 interrupt |

| 123       | exti_line11 interrupt |

| 124       | exti_line12 interrupt |

| 125       | exti_line13 interrupt |

| 126       | exti_line14 interrupt |

| 127       | exti_line15 interrupt |

| 128       | exti_line16 interrupt |

| 129       | Reserved              |

| 130       | Reserved              |

| 131       | Reserved              |

| 132       | Reserved              |

| 133       | Reserved              |

| 134       | Reserved              |

| 135       | Reserved              |

| 136       | Reserved              |

| 137       | Reserved              |

| 138       | Reserved              |

| 139       | Reserved              |

| 140       | Reserved              |

| 141       | Reserved              |

| 142       | Reserved              |

| 143       | Reserved              |

| 144       | Reserved              |

| 145       | Reserved              |

| 146       | Reserved              |

| Vector ID | Name                         |

|-----------|------------------------------|

| 147       | Reserved                     |

| 148       | Reserved                     |

| 149       | Reserved                     |

| 150       | Reserved                     |

| 151       | Reserved                     |

| 152       | Reserved                     |

| 153       | Reserved                     |

| 154       | Reserved                     |

| 155       | Reserved                     |

| 156       | Reserved                     |

| 157       | CAP6 HRcalibration interrupt |

| 158       | CAP7 HRcalibration interrupt |

| 159       | Reserved                     |

| 160       | SDFM1 interrupt              |

| 161       | Reserved                     |

| 162       | Reserved                     |

| 163       | Reserved                     |

| 164       | SDFM1 DR interrupt 1         |

| 165       | SDFM1 DR interrupt 2         |

| 166       | SDFM1 DR interrupt 3         |

| 167       | SDFM1 Dr interrupt 4         |

| 168       | Reserved                     |

| 169       | Reserved                     |

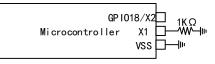

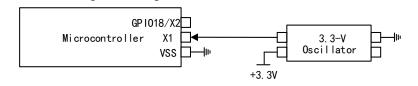

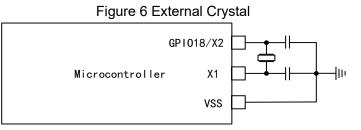

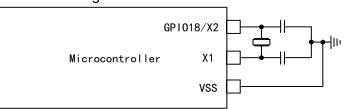

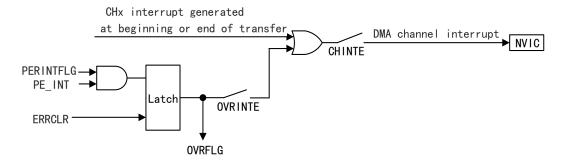

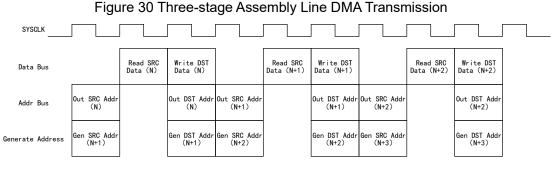

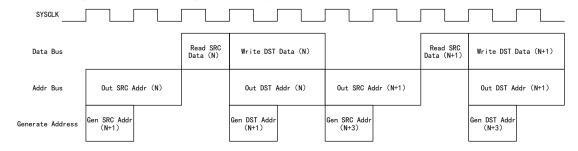

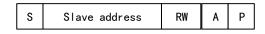

| 170       | Reserved                     |